### Description

The AL58263Q is an automotive AEC-Q100 grade 1 16-channel constant current LED driver with 16-bit grayscale Adaptive Pulse Density Modulation (APDM) PWM, supporting error diagnostics, power saving function and current gain control. This distinctive APDM technology abates the non-ideal IOUT distortion due to non-symmetric transient responses and enhances the refresh rate by separating efficiently the frame waveform.

The device operates over a 3V to 5.0V input voltage range, 15V output channel voltage, a fast 25MHz DCK input, and delivers up to 55mA of high accuracy current to each string of LED. Each channel average output current can be programmable independently via digital interface individually. All channels output current could be set by one external sensing resistor along with 6-bit global current control register.

The AL58263Q has built-in detection and diagnosis and LED open/short including error detection. Those errors results are stored in register for MCU to read out.

The AL58263Q is available in the Wettable Flank W-QFN4040-24/SWP (Type A1) package and specified over the -40°C to +125°C ambient temperature range.

### Features

- AEC-Q100 Grade 1

- Input Voltage VDD: 3V to 5.0V

- **Output Current Range**

- 2 to 55mA/5.0V

- ±0.1% (typ) Output Current Regulation

- 16 Constant-Current Sink Output Channel

- 16-Bit Grayscale Resolution

- 6-Bit Global Current Control

- 15V Rated Output Channels

- ±1.5% (typ) LED Current Accuracy Between Channels

- ±3% (typ) LED Current Accuracy Between Chips

- Stagger Outputs Delay for EMI Reduction

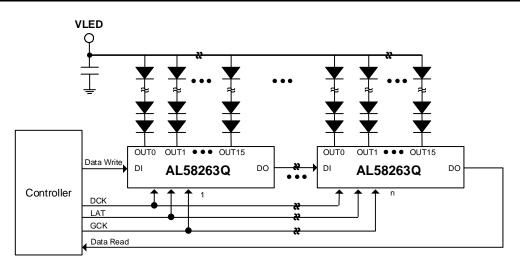

- Cascaded Capability (max 1,440 Devices)

- **Detection and Diagnosis**

- Error Detection Includes LED Open, LED Short, Output Port Leakage, Output Short-to-GND, Output Short-to-Power and **REXT Short-to-GND**

- Pre-Overtemperature Warning -

- 4-Wire Serial Interface +1 (LAT, DI, DO, DCK + GCK)

- 25MHz Data Clock (DCK) Frequency for Data Transfer

- Double Edge Gray Scale Clock up to 16MHZ (GCK)

- External GCK Watchdog Timer

- Zero Data and Sleep Mode for Power Saving

- **Register Programmable Options**

- Regular PWM or Adaptive Pulse Density Modulation

- Built Internal PWM or External Gray Scale Clock (GCK)

- Short Detection Threshold Voltage Selection (2/3/4/4.5V)

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- The AL58263Q is suitable for automotive applications requiring specific change control; this part is AEC-Q100 gualified, PPAP capable, and manufactured in IATF16949 certified facilities.

https://www.diodes.com/quality/product-definitions/

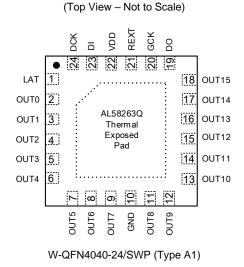

Pin Assignments

### Applications

- Automotive clusters

- Automotive local dimming displays

- Automotive front and back faceplates

- Automotive center stack displays

- Automotive interior and RGB lightings

- Automotive HVAC control panels

- Automotive gear shifter indicators

- Automotive exterior lightings

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

(3D Photo - Not to Scale)

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. Notes:

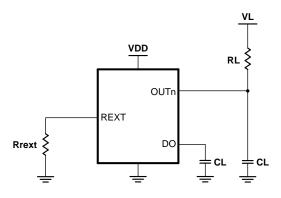

### **Typical Applications Circuit**

### **Pin Descriptions**

| Pin Name      | Pin Number<br>W-QFN4040-24/SWP<br>(Type A1) | Description                                                                                              |

|---------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|

| LAT           | 1                                           | Input terminal of data strobe and mode setting. Combine DCK with LAT signal to execute the mode control. |

| OUT0 to OUT15 | 2 to 9<br>and 11 to 18                      | Sink constant-current outputs (open-drain).                                                              |

| GND           | 10                                          | Ground terminal.                                                                                         |

| DO            | 19                                          | Serial data output terminal.                                                                             |

| GCK           | 20                                          | External double-edge grayscale clock input for APDM operations.                                          |

| REXT          | 21                                          | External resistors connected between REXT and GND for output current value setting.                      |

| VDD           | 22                                          | Supply voltage terminal.                                                                                 |

| DI            | 23                                          | Serial data input terminal.                                                                              |

| DCK           | 24                                          | Synchronous clock input terminal for serial data transfer. Data is sampled at the rising edge of DCK.    |

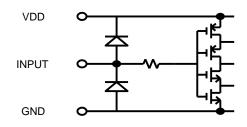

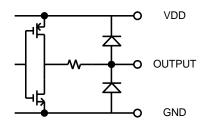

## **Equivalent Circuit of Inputs and Outputs**

2. DO Terminal

AL58263Q

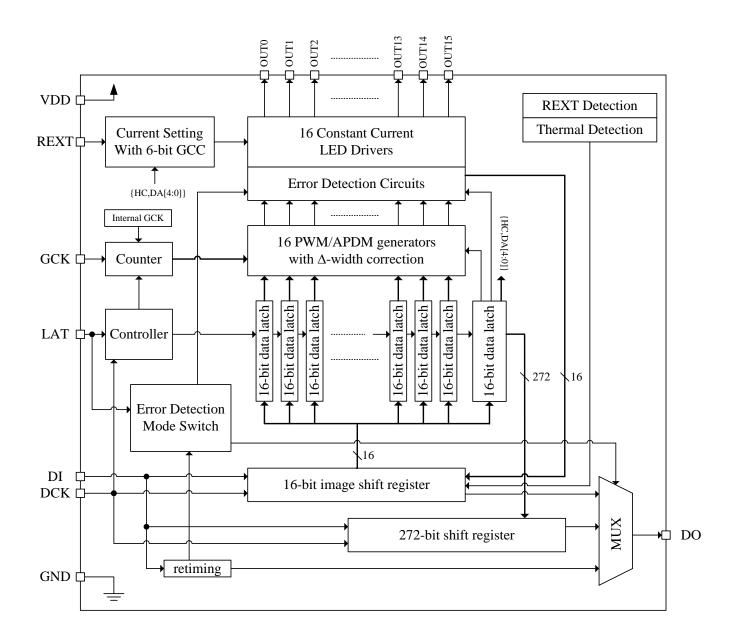

### **Functional Block Diagram**

### Absolute Maximum Ratings (Notes 4 & 5)

| Symbol                | Parameters                | Ratings                      | Unit |

|-----------------------|---------------------------|------------------------------|------|

| V <sub>DD</sub>       | Supply Voltage            | -0.3 to 7.0                  | V    |

| Vdi, Vdck, Vgck, Vlat | Input Voltage             | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Ιουτ                  | Output Current            | 60                           | mA   |

| Vout                  | Output Voltage            | -0.3 to 16                   | V    |

| f <sub>DCK</sub>      | Input Clock Frequency     | 25                           | MHz  |

| fgcк                  | Input Grayscale Frequency | 16                           | MHz  |

| Ignd                  | GND Terminal Current      | 960                          | mA   |

Notes: 4. Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings for extended periods can affect device reliability.

5. All voltage values are with respect to ground terminal.

### **ESD** Ratings

| Symbol | Parameter                  | Value | Unit |

|--------|----------------------------|-------|------|

|        | Human Body Model (HBM)     | 2000  | V    |

| Vesd   | Charged Device Model (CDM) | 750   | V    |

| Symbol           | Parameter                                    | Value | Unit |

|------------------|----------------------------------------------|-------|------|

| R <sub>0JA</sub> | Junction-to-Ambient Thermal Resistance       | 31.16 | °C/W |

| ReJC(top)        | Junction-to-Case (Top) Thermal Resistance    | 17.25 | °C/W |

| Rөjb             | Junction-to-Board Thermal Resistance         | 9.34  | °C/W |

| $\Psi_{JT}$      | Junction-to-Top Characterization Parameter   | 0.41  | °C/W |

| $\Psi_{JB}$      | Junction-to-Board Characterization Parameter | 9.14  | °C/W |

| ReJC(bot)        | Junction-to-Case (Bottom) Thermal Resistance | 3.33  | °C/W |

Note: 6. Measured on EIA/JESD51-7, 4-layer PCB. For better thermal performance, larger copper pad for heatsink is needed.

### **Recommended Operating Conditions**

| Symbol          | Parameter                    | Min | Тур | Max  | Unit |

|-----------------|------------------------------|-----|-----|------|------|

| V <sub>DD</sub> | Operating Supply Voltage     | 3.0 | 3.3 | 5.0  | V    |

| Ιουτ            | Output Current (Note 7)      | 2   | —   | 55   | mA   |

| Vout            | Output Voltage               | 1   | _   | 15   | V    |

| TA              | Ambient Temperature (Note 7) | -40 | —   | +125 | °C   |

| TJ              | Junction Temperature         | -40 | _   | +150 | °C   |

| Tstg            | Storage Temperature          | -55 | _   | +150 | °C   |

Note: 7. Dependent on ambient temperature, LED voltage, package thermal limitation, and PCB layout.

### Electrical Characteristics (V<sub>DD</sub> = 5.0V @T<sub>A</sub> = -40°C to +125°C, unless otherwise specified.)

| Characteristic                                       | Symbol              | Condition                                             | Min                | Тур  | Max                | Unit    |

|------------------------------------------------------|---------------------|-------------------------------------------------------|--------------------|------|--------------------|---------|

| Input Voltage "H" Level                              | VIH                 | CMOS logic level                                      | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V       |

| Input Voltage "L" Level                              | VIL                 | CMOS logic level                                      | GND                | _    | 0.3V <sub>DD</sub> | V       |

| Output Leakage Current                               | Ilk                 | Vout = 15V                                            | _                  |      | 0.2                | μA      |

|                                                      | lol                 | Vol = 0.4V                                            | 1                  | 3.4  | 5                  |         |

| Driving Current (DO)                                 | I <sub>OH</sub>     | $V_{OH} = V_{DD}$ -0.4                                | -5                 | -3.4 | -1                 | mA      |

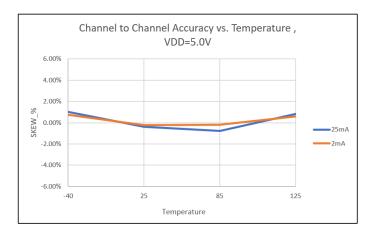

| Output Current Skew<br>(Channel-to-Channel) (Note 8) | dlout1              | V <sub>OUT</sub> = 1.0 V<br>R <sub>REXT</sub> = 560Ω  | _                  | ±1.5 | ±3.5               | %       |

| Output Current Skew<br>(Chip-to-Chip) (Note 9)       | dlout2              | GCC = 101011<br>$T_J = +25^{\circ}C$                  | _                  | ±3   | ±6                 | %       |

| Output Voltage Regulation (Note 10)                  | % / Vout            | $R_{REXT} = 560\Omega$<br>Vout = 1V to 3V             | _                  | ±0.1 | ±.1                | 97 / 17 |

| Supply Voltage Regulation (Note 11)                  | % / V <sub>DD</sub> | $R_{REXT} = 560\Omega$ $V_{DD} = 3V \text{ to } 5.0V$ | —                  | ±0.6 | ±1                 | % / V   |

| Supply Current (Note 12)                             | IDD1(off)           | $R_{REXT} = 560\Omega$<br>All outputs turn off        | 1                  | 5.5  | 9.7                | m (     |

| Supply Current (Note 12)                             | IDD2(on)            | $R_{REXT} = 560\Omega$<br>All outputs turn on         | 1                  | 5.5  | 9.7                | mA      |

| Thermal Alarm Temperature                            | T <sub>AL</sub>     | _                                                     | _                  | +155 | _                  | °C      |

| Thermal Alarm Temperature Hysteresis                 | TAL_HYS             | _                                                     | _                  | +15  | _                  | °C      |

Notes: 8. Channel-to-channel skew is defined by the formula below:

$$\Delta(\%) = \left[ \frac{Iout_n}{(Iout_0 + Iout_1 + \dots + Iout_{15})} - 1 \right] * 100\%$$

16

9. Chip-to-Chip skew is defined by the formula below:

$$\Delta(\%) = \begin{bmatrix} \frac{(Iout_0 + Iout_0 + ... + Iout_{15})}{16} - (Ideal Current at Temperature) \\ (Ideal Current at Temperature) \end{bmatrix} * 100\%$$

10. Output voltage regulation is defined by the formula below:

$$\Delta(\%/V) = \left[ \frac{Iout_n @Vout_n = 3V) - Iout_n @Vout_n = 1V)}{Iout_n (@Vout_n = 3V)} \right] * \frac{100\%}{3V - 1V}$$

11. Supply voltage regulation is defined by the formula below:

$$\Delta(\%/V) = \left[ \frac{Iout_n (@V_{DD} = 5.5V) - Iout_n (@V_{DD} = 3V)}{Iout_n (@Vcc = 3V)} \right] * \frac{100\%}{5.5V - 3V}$$

12. IO excluded.

| Characteristic                 | :      | Symbol              | Condition                                          | Min | Тур  | Мах     | Unit |

|--------------------------------|--------|---------------------|----------------------------------------------------|-----|------|---------|------|

| Propagation Delay ('L' to 'H') | DCK-DO | t <sub>P</sub> LH3  |                                                    | _   | 30   | 60      |      |

| Propagation Delay ('H' to 'L') | DCK-DO | tPHL3               |                                                    | _   | 30   | 60      |      |

|                                | LAT    | tw(LAT)             |                                                    | 50  | _    |         |      |

| Pulse Duration                 | GCK    | tw(gcк)             |                                                    | 20  | _    |         |      |

|                                | DCK    | tw <sub>(DCK)</sub> |                                                    | 20  | _    |         |      |

| Cotup Timo                     | LAT    | tsu(LAT) 20         | 20                                                 | _   |      |         |      |

| Setup Time                     | DI     | tsu(D)              | V <sub>IH</sub> = V <sub>DD</sub><br>VIL = GND     | 5   | _    |         | ns   |

| Hold Time                      | LAT    | th <sub>(LAT)</sub> | $R_{REXT} = 560\Omega$                             | 20  | _    |         |      |

| Hold Time                      | DI     | th(D)               | V <sub>L</sub> = 5.0V                              | 5   | _    |         |      |

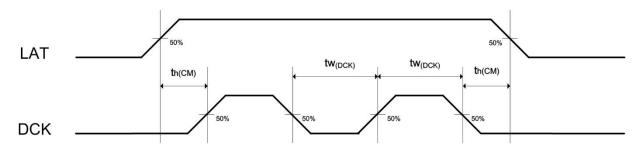

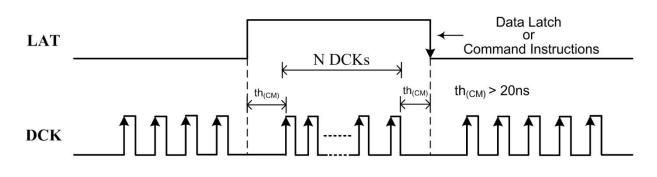

| Hold Time of Instruction       |        | th(CM)              | − R <sub>L</sub> = 150Ω<br>_ C <sub>L</sub> = 13pF | 20  | _    | _       |      |

| LED Error Detection Time       |        | terr1               |                                                    | 500 | _    | _       |      |

| Short-to-Ground Detection Time |        | terr3               |                                                    | 500 | _    |         |      |

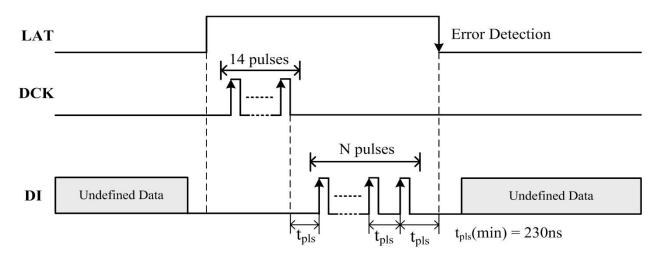

| Interval Between Two Command   | tpls   |                     | 230                                                | 250 |      |         |      |

| Wake-up Time from Sleep or 0-D | twake  | ]                   | _                                                  |     | 4000 | μs      |      |

| Data Clock Frequency           | fdck   | ]                   | _                                                  |     | 25   | N 41 1- |      |

| Grayscale Clock Frequency (Dou | fgcк   | 1                   | _                                                  | _   | 16   | MHz     |      |

### Switching Characteristics (V<sub>DD</sub> = 5.0V @T<sub>A</sub> = -40°C to +125°C, unless otherwise specified.) (Guaranteed by design)

### **Switching Characteristics Test Circuit**

Switching Characteristics Test Circuit

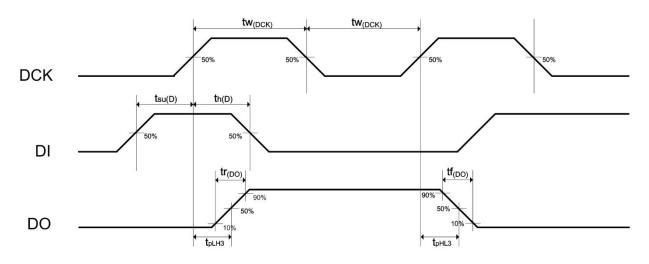

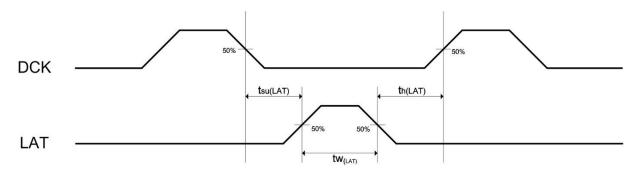

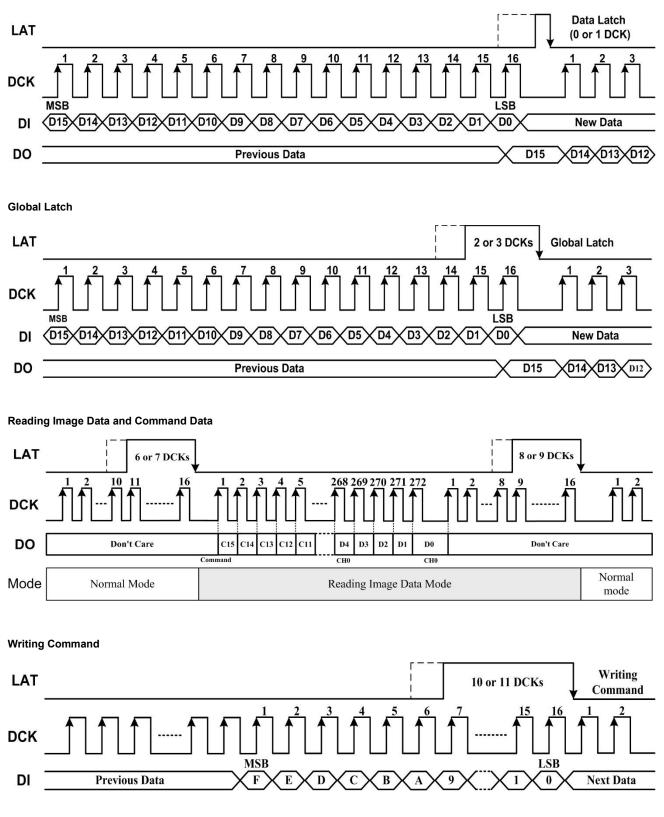

### **Timing Characteristics**

#### Timing Diagram

1. DCKI-DI, DO

2. GCK-LAT

3. LAT-DCK (Instruction)

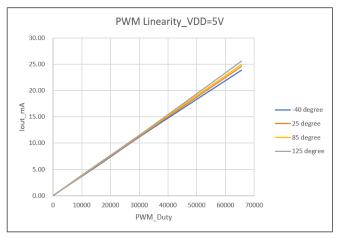

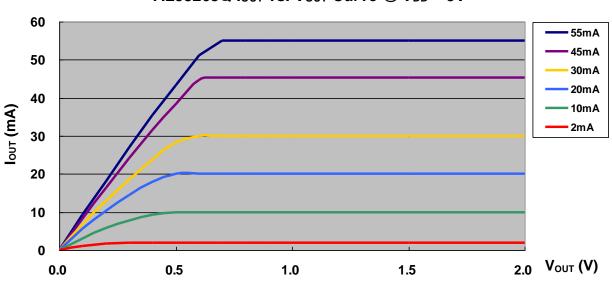

### Typical Performance Characteristics (V<sub>DD</sub> = 5V, -40°C < T<sub>A</sub> < +125°C, unless otherwise specified.)

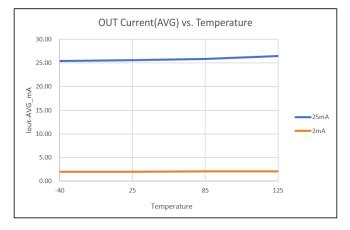

### Figure 2. Output Current (AVG) vs. Temperature

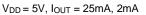

#### Figure 3. Gain Control Current vs. Temperature

### **Functional Descriptions**

#### **Fast Transient Response**

The AL58263Q supports the fast transient response to make high image resolution possible. The GCK period of 50ns is enough to get a complete Vour waveform.

#### **Stagger Outputs Delay**

Large inrush currents will be induced when the system activates all the outputs at once. To reduce this interference of EMI, the AL58263Q is designed to have a constant length of delay time (around 16ns) between two output groups. The first group is OUT2n and the second group is OUT2n+1 (n = 0 to 7).

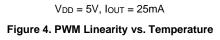

#### **Global Current Control (GCC)**

The AL58263Q provides 6bits global current control (GCC) which could adjust the output current by 64 steps.

The GCC bits are included in the command data defined as follows:

| F | E | D | С | В | А | 9  | 8   | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|----|-----|-----|-----|-----|-----|---|---|---|---|

| — | _ |   |   |   |   | HC | DA4 | DA3 | DA2 | DA1 | DA0 |   |   |   |   |

The relationship between the Gain value and GCC bits is described below:

HC = 1, Gain =  $(3 \times D + 33) / 65 \times (1-0.001 \times D)$ , the gain range is from 0.508 to 1.878

HC = 0, Gain = (3 x D + 32) / 256 x (1-0.0006 x D), the gain range is from 0.125 to 0.479

Where D = DA4 x  $2^4$  + DA3 x  $2^3$  + DA2 x  $2^2$  + DA1 x  $2^1$  + DA0 x  $2^0$

For example, HC = 1 and DA[4:0] = 11000

$D = 1x 2^4 + 1 x 2^3 + 0 x 2^2 + 0 x 2^1 + 0 x 2^0 = 24$

Gain = (3 x 24 + 33) / 65 x (1-0.001 x 24) = 1.577

#### **Reference Resistor**

The constant current values are determined by an external resistor placed between REXT pin and GND pin. The following formula is utilized to calculate the current value:

$I_{OUT}$  (mA) = 13.45 /  $R_{REXT}(k\Omega)$  x Gain

This 13.45 constant center at 10mA may need to be adjusted slightly based on users' application and test conditions. Where R<sub>REXT</sub> is a resistor placed between REXT and GND.

For example, I<sub>OUT</sub> is around 24.12mA when  $R_{REXT} = 560\Omega$  and with GCC = 101011

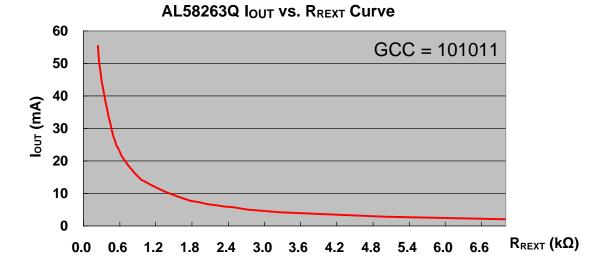

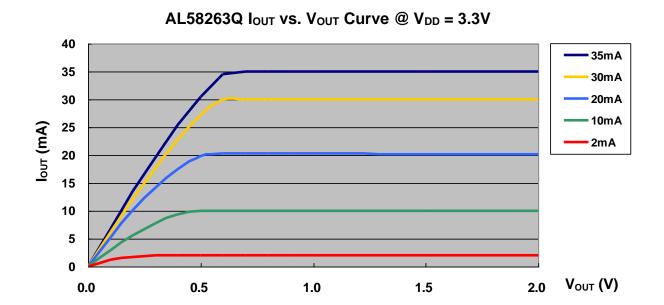

#### **Constant-Current Output**

The current characteristics could maintain invariable in the influence of loading voltage. Therefore, the AL58263Q could minimize the interference of different LED forward voltages and produce the constant current. The following figures illustrating the suitable output voltage should be determined in order to keep an excellent performance.

AL58263Q IOUT VS. VOUT Curve @ VDD = 5V

#### **Control Instructions**

| Instruction Name                       | Number of DCK Pulses<br>when LAT is at High | Function Description                                                                                                                                         |

|----------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Latch                             | 0 or 1                                      | Strobes image data into temporary registers. In this time, constant current outputs are not updated to a new frame data.                                     |

| Global Latch                           | 2 or 3                                      | Strobes image data from temporary registers into an APDM/PWM generator. In this time, constant current outputs are updated to a new frame data.              |

| Reading Image Data<br>and Command Data | 6 or 7                                      | Read out image data and command data from the latch cell to the 272bits shift registers. And the read data could shift out from DO pin by serial DCK pulses. |

| Return to Normal Mode                  | 8 or 9                                      | Switch Back from the reading data mode to the normal operating mode.                                                                                         |

| Writing Command                        | 10 or 11                                    | Strobes command data from the 16bits shift register into the command latch cell.                                                                             |

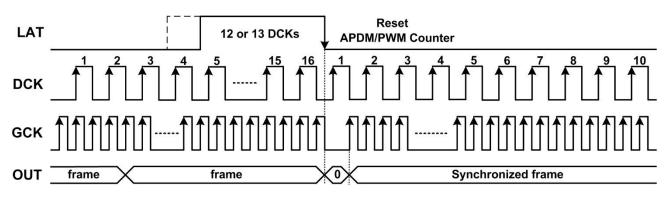

| Reset<br>APDM/PWM Counter              | 12 or 13                                    | This instruction will reset APDM/PWM counter to synchronize a new<br>frame if CMD[11] = "H".                                                                 |

#### Data Latch

Reset APDM/PWM Counter (Set CMD[11] = "1")

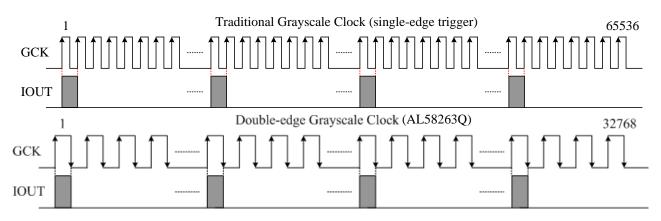

#### EMI Reduction Grayscale Clock (Double-Edge Grayscale Clock)

A whole period of 16bits resolution must be composed by 65536 traditional grayscale clocks because constant current outputs only are triggered at the rising edge of clocks. Therefore, a controller has to transmit fast grayscale clocks in order to accomplish high refresh rate when users adopt traditional PWM chips. The AL58263Q supports a specific mode of double-edge grayscale clocks which trigger both at rising and falling edges of clocks. By this approach, a whole period of 16bits resolution is composed by only 32768 double-edge grayscale clocks and the electromagnetic interference would be decreased substantially due to slow grayscale clocks.

#### **Command Data Format**

\_

| CMD[0]   | CMD[1] | CMD[2]  | CMD[3]  | CMD[4]  | CMD[5]  | CMD[6]  | CMD[7]  |

|----------|--------|---------|---------|---------|---------|---------|---------|

| 0        | 1      | 2       | 3       | 4       | 5       | 6       | 7       |

| Watchdog | Sleep  | Vth<0>  | Vth<1>  | DA0     | DA1     | DA2     | DA3     |

|          |        |         |         |         |         |         |         |

| CMD[8]   | CMD[9] | CMD[10] | CMD[11] | CMD[12] | CMD[13] | CMD[14] | CMD[15] |

| 9 A B C D E F DO                                          | 9 A          | 8   |

|-----------------------------------------------------------|--------------|-----|

| HC Data Syn Counter<br>Reset PWM GCK REXT Data<br>Loading | 4 HC Data Sy | DA4 |

| CMD Bit   | Initial Value | Value                            | Function                     | Description                                                                                                                                                                                                   |

|-----------|---------------|----------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

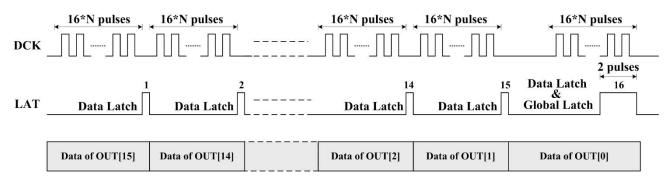

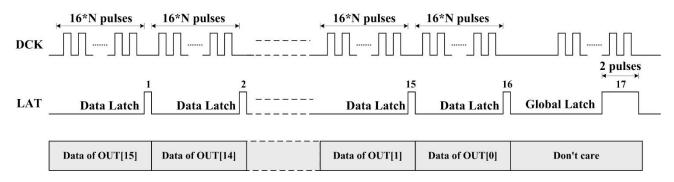

| CMD[15]   | 1'b0          | 1'b0                             | Mode0                        | Data transmitting format:<br>15 times of data latch + one global latch                                                                                                                                        |

| 01112[10] | 150           | 1'b1                             | Mode1                        | Data transmitting format:<br>16 times of data latch + one global latch                                                                                                                                        |

| CMD[14]   | 1'b0          | 1'b0                             | Enable                       | When the voltage of REXT is below 0.15V, all outputs will be forced off.                                                                                                                                      |

| [···]     |               | 1'b1                             | Disable                      | Disable                                                                                                                                                                                                       |

|           |               | 1'b0                             | External GCK                 | The GCK signal stems from an external source.                                                                                                                                                                 |

| CMD[13]   | 1'b0          | 1'b1                             | Internal GCK                 | The GCK signal stems from an internal oscillator, typ<br>1.7MHz at 3.3V and 2.8MHz at 5V<br>(When CMD[13] = "1", please set CMD[0] = "0")                                                                     |

|           |               | 1'b0                             | APDM Mode                    | Enter the PWM mode to abate the transient loss when<br>– AL58263Q is as a PWM generator.                                                                                                                      |

| CMD[12]   | 1'b0          | 1'b1                             | PWM Mode                     | when CMD[12] = 1'b0 => APDM mode<br>when CMD[12] = 1'b1 => PWM mode                                                                                                                                           |

|           |               | 1'b0                             | Disable                      | Disable                                                                                                                                                                                                       |

| CMD[11]   | 1'b0          | 1'b1                             | Enable                       | Execute counter reset by inserting 12 or 13 DCKs (rising edge) when LAT keeps at high.                                                                                                                        |

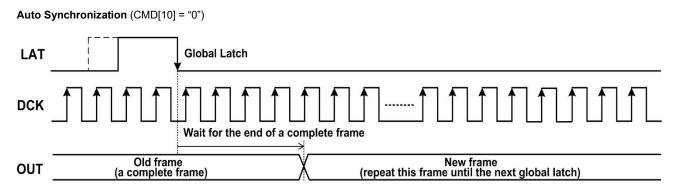

| CMD[10]   | 1'b0          | 1'b0                             | Auto<br>Synchronization      | When the device receives a latch signal, the new frame is updated until the end of old frame.                                                                                                                 |

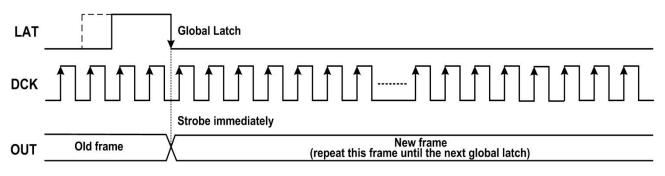

| CINID[10] | 100           | 1'b1                             | Manual<br>Synchronization    | When the device receives a latch signal, the new frame is updated immediately                                                                                                                                 |

| CMD[9:4]  | 6'b101011     | 6'b000000 to<br>6'b111111        | G.C.C                        | 6bits DA data for global current control<br>(Allow 64-step programmable current gain)                                                                                                                         |

| CMD[3:2]  | 2'b00         | 2'b00<br>2'b01<br>2'b10<br>2'b11 | 2.0V<br>3.0V<br>4.0V<br>4.5V | Threshold voltage for LED short detection (Both at $V_{DD}$ = 5V and 3.3V)                                                                                                                                    |

|           | 1'b0          | 1'b0                             | Disable                      | Enter 0-data power saving mode                                                                                                                                                                                |

| CMD[1]    | 001           | 1'b1                             | Enable                       | when 16bits PWM data of 16ch are all zeros.                                                                                                                                                                   |

|           |               | 1'b0                             | Disable                      | GCK watchdog<br>All IOUTs will be turned off automatically when GCK                                                                                                                                           |

| CMD[0]    | 1'b0          | 1'b1                             | Enable                       | <ul> <li>All IOO's will be turned on automatically when GCK</li> <li>keeps high or low level over 30ms.</li> <li>(Result can be read out by "Thermal Detection Mode" or<br/>"Rext Detection Mode")</li> </ul> |

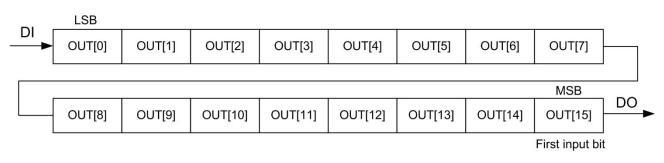

#### Image Data Format

16bits APDM/PWM data are transmitted into the 16bits shift register according to the format illustrated above. The first input bit is the most significant bit of each channel.

#### Data Transmitting Protocol

#### **MODE0** (CMD[15] = "0")

This data transmitting mode is comprised of 15 data latches and one global latch. The first data latch strobes image data for OUT[15]. And the last global latch strobes image data for OUT[0] and loads all image data of 16 channels into the APDM/PWM generator. N is the number of devices in series.

#### MODE1 (CMD[15] = "1")

This data transmitting mode is comprised of 16 data latches and one global latch. The first data latch strobes image data for OUT[15]. And the last global latch loads all image data of 16 channels into the APDM/PWM generator but doesn't strobe any image data for output channels. N is the number of devices in series.

#### Data Synchronization

The AL58263Q could abate the grayscale loss during the renewal of frame by this approach of auto synchronization. When the command bit CMD[10] is set to "0", this function could be executed automatically. After a global latch, all OUTs would accomplish a complete frame of old data and then update new frame data. Therefore, each frame maintains the fixed time and the assigned grayscale. A controller just provides a free-running GCK for grayscale display in this mode.

#### Manual Synchronization (CMD[10] = "1")

When the command bit CMD[10] is set to "1", the new frame data would be updated immediately. The old frame loses probably a little grayscale due to a non-complete frame time. In this mode, a controller must calculate carefully the number of GCKs in order to synchronize a frame.

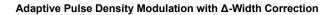

Adaptive Pulse Density Modulation (APDM) is a technique to improve output current waveform distortion and increase visual refresh rate. The adaptive output waveform is determined automatically by the grayscale value. When all outputs operate at high grayscale resolution (grayscale resolution  $\geq$  50%), the output waveform is divided into 128 segments to increase visual refresh rate. Otherwise, the output waveform is divided into 64 segments at low grayscale resolution to improve output current waveform distortion. And the  $\Delta$ -width correction ( $\Delta \neq 0$ ) is used to compensate the non-ideal output current transient response.

When CMD[12] = "0", the output waveform operates according to APDM.

When CMD[12] = "1", the output waveform is a form of non-scrambling PWM in order to drive high power LED and decrease the transient loss.

#### **Diagnosis and Protections**

#### **Error Detection Mode Instructions**

| Instruction Name                              | Number of DI Pulses when LAT is at High | Function Description                                                                                                                                                                                                                       |

|-----------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

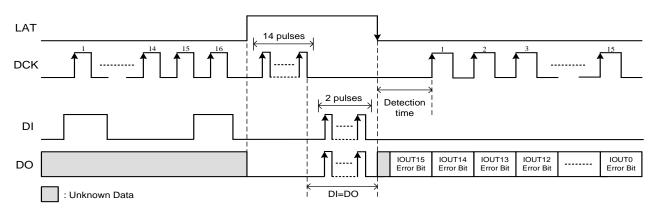

| LED Open Detection                            | 2                                       | Execute the LED Open Detection no matter what the image data is. The image strobe will occur at the falling edge of LAT signal.                                                                                                            |

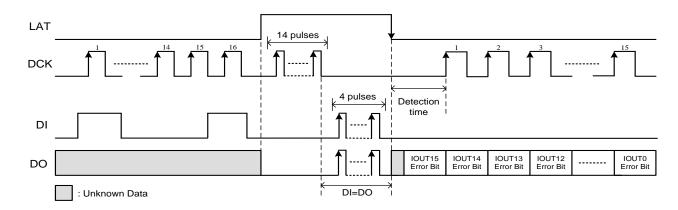

| LED Short Detection                           | 4                                       | Execute the LED Short Detection no matter what the image data is. The image strobe will occur at the falling edge of LAT signal.                                                                                                           |

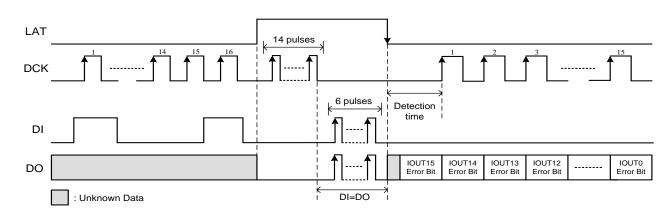

| Short-to-GND Detection                        | 6                                       | Execute the Short-to-GND Detection no matter what the image data is. The device will detect each IOUT pin if short-to-ground or not. The image strobe will occur at the falling edge of LAT signal.                                        |

| Thermal Detection & Watchdog Result Read Out  | 8                                       | The device will load thermal detection result and watchdog detection result into the 16 <sup>th</sup> and 1 <sup>st</sup> image shift register by this instruction. The thermal error occurs when the junction temperature is over +155°C. |

| LED Smart Detection                           | 10                                      | Execute the LED Smart Detection no matter what the image data is. The device will detect LED Open and LED Short error simultaneously by this instruction. The image strobe will occur at the falling edge of LAT signal.                   |

| Sleep Mode                                    | 12                                      | This instruction forces the device into Sleep Mode at the falling edge of LAT signal, then keeps GCK = high most internal circuits will shut down. The device will be activated in the following LAT signal.                               |

| REXT Pin Detection & Watchdog Result Read Out | 14                                      | The device will load REXT detection result and watchdog detection result into the 16 <sup>th</sup> and 1 <sup>st</sup> image shift register by this instruction. The REXT error occurs when the REXT pin is short-to-GND or above 2.5V.    |

#### **Diagnosis and Protections (continued)**

#### Error Bit

| Error Bit | Symbol | Description                                                                                                                                                                                                     |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Error  | When errors, such as open errors, short errors, short-to-GND errors, and thermal errors (PreOTP), are detected in the channel, the error bit, zero, will be loaded into the corresponding image shift register. |

| 1         | Normal | In the detecting mode, the bit, one, will be loaded into the corresponding image shift register if the device is under normal operating conditions.                                                             |

#### LED Open Error Detection

When the LED open error detection instruction is executed, it is necessary to input two DI pulses in the Error Detection Mode. No matter what the image latch data is, the output ports of the AL58263Q will turn on with 0.1mA for error detection. The detection time is defined from the falling edge of LAT to the rising edge of following DCK.

When the voltage of IOUT pins is below 0.3V, the error bit, zero, will be loaded into the corresponding image shift register. The error bit will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications.

#### **Diagnosis and Protections (continued)**

#### LED Short Error Detection (Output Short-to-Power Included)

When the LED short error detection instruction is executed, it is necessary to input four DI pulses in the Error Detection Mode. No matter what the image latch data is, the output ports of the AL58263Q will turn on with 0.1mA for error detection. The detection time is defined from the falling edge of LAT to the rising edge of following DCK. When the voltage of IOUT pins is above the threshold voltage of LED short detection determined by CMD[14:13], the error bit, zero, will be loaded into the corresponding image shift register. The error bit will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications.

#### Short-to-GND Error Detection (Output Port Leakage Included)

When the short-to-GND error detection instruction is executed, it is necessary to input six DI pulses in the Error Detection Mode. No matter what the image latch data is, this instruction forces the output ports of the AL58263Q to turn off for error detection. The detection time is defined from the falling edge of LAT to the rising edge of following DCK.

When the voltage of IOUT pins is below 0.3V, the error bit, zero, will be loaded into the corresponding image shift register. The error bit will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications.

#### **Diagnosis and Protections (continued)**

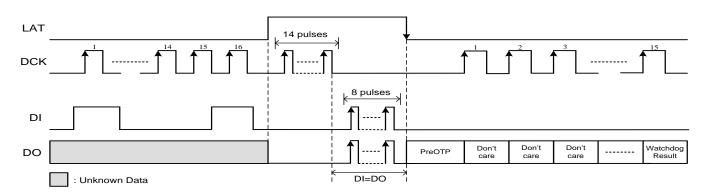

#### Pre-OTP Warning - Thermal Detection & Watchdog Result Read Out

The AL58263Q has pre-thermal warning threshold of +155°C (typical).

When the thermal detection instruction is executed, it is necessary to input eight DI pulses in the Error Detection Mode. AL58263Q will judge of junction temperature by the instruction. If the junction temperature is over +155°C, it will lead to thermal error. The device will load the PreOTP and watchdog result into the 16<sup>th</sup> and 1<sup>st</sup> image shift register and fill out the other image shift registers with bit code, 1. The error report will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications. When CMD[0] = 1 and GCK keeps low or high over 30ms, the watchdog result would be "0", otherwise it would be "1".

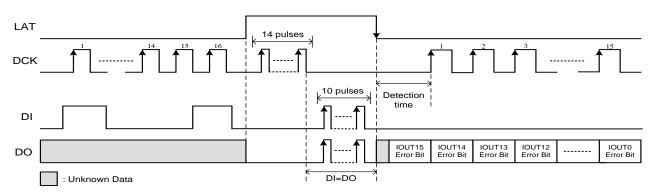

#### **LED Smart Detection**

When the LED smart detection instruction is executed, it is necessary to input ten DI pulses in the Error Detection Mode. No matter what the image latch data is, the output ports of the AL58263Q will turn on with 0.1mA for error detection. The detection time is defined from the falling edge of LAT to the rising edge of following DCK. When the voltage of IOUT pins is below 0.3V for LED open detection or above the threshold voltage of LED short detection determined by CMD[14:13], the error bit, zero, will be loaded into the corresponding image shift register. The error bit will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications.

#### **Diagnosis and Protections (continued)**

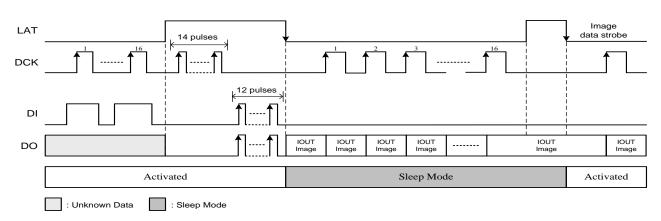

#### Sleep Mode

For power saving, the AL58263Q supports the sleep mode to turn off most circuits. It is necessary to input twelve pulses in the Error Detection Mode to execute this instruction and then keeps GCK = high at sleep mode. In the sleep mode, the supply current maintains < 0.1mA because most analog circuits are shut down, but the digital interface is still activated in order to receive external digital data. The AL58263Q will enter sleep mode at the falling edge of this LAT signal and revive at the falling edge of following LAT signal. The serial image data will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications.

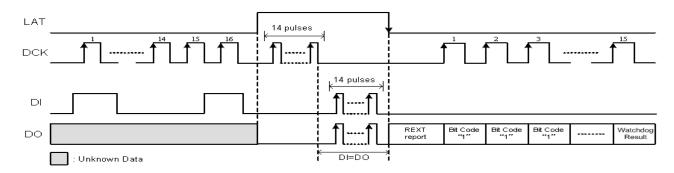

#### **REXT Detection & Watchdog Result Read Out**

When the REXT detection instruction is executed, it is necessary to input fourteen DI pulses in the Error Detection Mode. The AL58263Q will detect the voltage of REXT pin by the instruction. If the REXT pin is open or above 2.5V or below 0.15V, it will lead to REXT error. The device will load the REXT report and watchdog result into the 16<sup>th</sup> and 1<sup>st</sup> image shift register and fill out the other image shift registers with bit code, 1. The error report will be shifted out from the DO pin on the synchronization of the rising edge of DCK. And a retiming DO signal, which is similar to DI signal, appears when the LAT signal stays in high level for cascading applications. When CMD[0] = 1 and GCK keeps low or high over 30ms, the watchdog result would be "0", otherwise it would be "1".

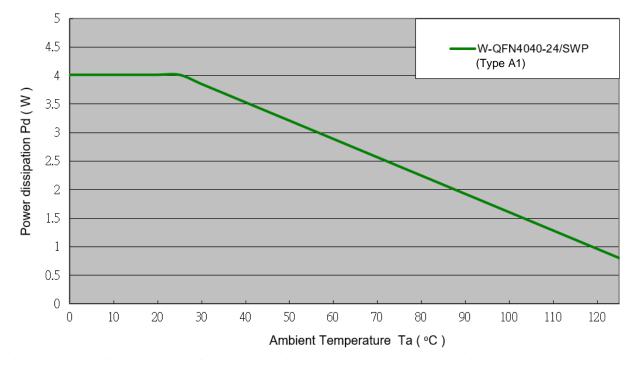

#### **Power Dissipation**

When the 16 output channels are turned on, the practical power dissipation is determined by the following equation:

$$PD$$

(practical) =  $VDD \times IDD + VOUt_{(0)} \times IOut_{(0)} \times Duty_{(0)} + \dots + VOUt_{(N)} \times IOut_{(N)} \times Duty_{(N)}$ , where  $N=1$  to 15

In secure operating conditions, the power consumption of an integrated chip should be less than the maximum permissible power dissipation which is determined by the package types and ambient temperature. The formula for maximum power dissipation is described as follows:

$$PD(max) = \frac{Tj(max)(\ \C) - Ta(\ \C)}{Rth(i-a)(\ \C/Watt)}$$

The PD(max) declines as the ambient temperature raises. Therefore, suitable operating conditions should be designed with caution according to the chosen package and the ambient temperature. The following figure illustrates the relation between the maximum power dissipation and the ambient temperature.

### Maximum Power Dissipation v.s. Ambient Temperature

#### Design Tools (Note 13)

- AL58263Q Demo Boards

- AL58263Q Calculator

- Demo Board Gerber File for PCB Layout Reference

Note: 13. Diodes Incorporated's design tools can be found on our website at https://www.diodes.com/design/tools/.

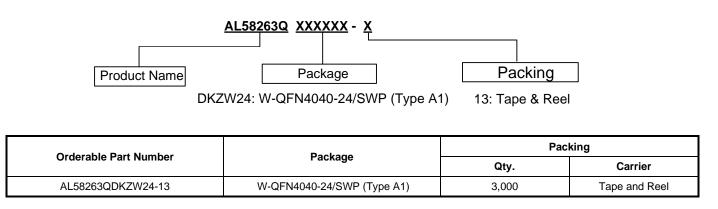

### **Ordering Information**

### **Marking Information**

| (Top View) |                                      |

|------------|--------------------------------------|

|            | XXX : Identification Code            |

| XXX        | Y : Year : 0 to 9 (ex: 4 = 2024)     |

| YWX        | W : Week : A to Z : week 1 to 26;    |

| YVVX       | a to z : week 27 to 52; z represents |

|            | week 52 and 53                       |

|            | X : Internal Code                    |

| Orderable Part Number | Package                    | Identification Code |

|-----------------------|----------------------------|---------------------|

| AL58263QDKZW24-13     | W-QFN4040-24/SWP (Type A1) | J7Q                 |

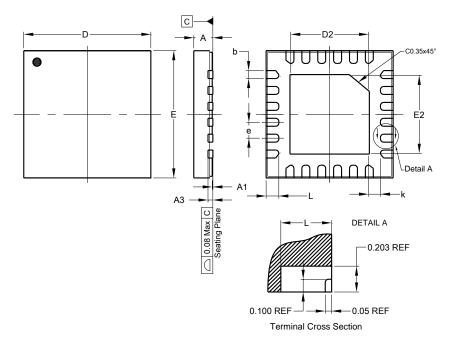

### **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

W-QFN4040-24/SWP (Type A1)

| W-QFN4040-24/SWP     |            |      |      |  |  |  |

|----------------------|------------|------|------|--|--|--|

| (Type A1)            |            |      |      |  |  |  |

| Dim                  | Min        | Max  | Тур  |  |  |  |

| Α                    | 0.70       | 0.80 | 0.75 |  |  |  |

| A1                   | 0.00       | 0.05 | 0.02 |  |  |  |

| A3                   | 0.203 REF  |      |      |  |  |  |

| b                    | 0.18       | 0.30 | 0.25 |  |  |  |

| D                    | 3.90       | 4.10 | 4.00 |  |  |  |

| D2                   | 2.45       | 2.55 | 2.50 |  |  |  |

| Е                    | 3.90       | 4.10 | 4.00 |  |  |  |

| E2                   | 2.45       | 2.55 | 2.50 |  |  |  |

| е                    | e 0.50 BSC |      |      |  |  |  |

| k                    | 0.20       |      |      |  |  |  |

| L                    | 0.35       | 0.45 | 0.40 |  |  |  |

| All Dimensions in mm |            |      |      |  |  |  |

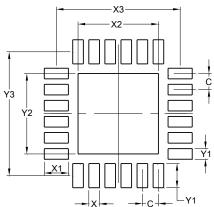

### **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

# W-QFN4040-24/SWP (Type A1)

| Dimensions | Value<br>(in mm) |  |

|------------|------------------|--|

| С          | 0.500            |  |

| Х          | 0.300            |  |

| X1         | 0.750            |  |

| X2         | 2.500            |  |

| X3         | 3.850            |  |

| Y          | 0.750            |  |

| Y1         | 0.300            |  |

| Y2         | 2.500            |  |

| Y3         | 3.850            |  |

### **Tape and Reel Information**

Please see https://www.diodes.com/assets/Packaging-Support-Docs/AP02007.pdf for tape and reel details.

### **Mechanical Data**

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per JESD22-B102 (3)

- Weight: 0.037 grams (Approximate)

#### **IMPORTANT NOTICE**

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<u>https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</u>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com