#### IntelliFET HIGH-SIDE POWER SWITCH

### **Description**

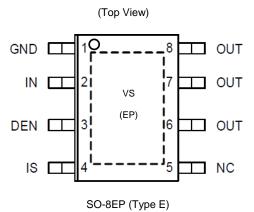

The ZXMS81200SP is a single-channel, high-side power switch in a SO-8EP (Type E) exposed heatsink package incorporating protective and diagnostic functions.

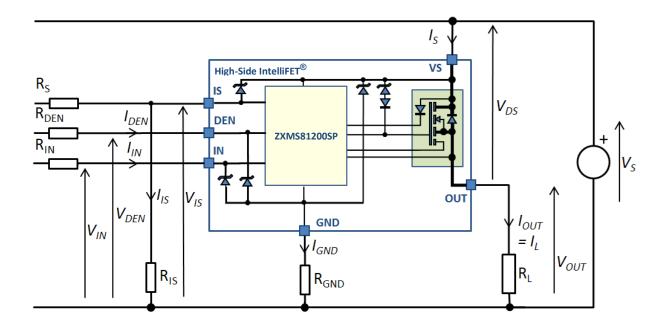

The device comprises a monolithic n-channel vertical power MOSFET with integrated temperature and current sensors with a charge-pumped gate supply and has a low quiescent current in OFF state.

The device is enabled by active high 3.3V and 5V logic-level drive to the inputs. The device includes a diagnostic current-sense output proportional to load current and a defined diagnostic fault signal in case of overload operation, overtemperature, short-circuit or open-load conditions.

### **Pin Assignment**

#### **Features**

#### **Protection Functions**

- Reverse Battery Protection Using External Components

- Voltage Dependent Current Limiting

- Overtemperature Protection with Auto-Restart

- Overvoltage Protection Including Load Dump

- Stable Undervoltage Protection

- ESD Protection

- Loss of Ground Protection with External Components

- Enhanced Short-Circuit Protection

#### **Diagnostic Functions**

- Proportional Load Current-Sense Output

- Linear Voltage Drop Regulation to Maintain Sense Accuracy Even at Very Low Load Currents

- Enabled by Logic Input

- Defined Temperature and Current Dependency

- Open-Load Detection

- Using Load Current-Sense in ON State

- Using Output Voltage Detection in OFF State

- Defined Fault Signal in Case of Overload Operation,

Overtemperature, or Short-Circuit and Open-Load in OFF State

# **Applications**

- High-side switching with diagnostic feedback for:

- 12V grounded loads

- Resistive, inductive and capacitive loads

- Suitable for high inrush current loads

- Incandescent lamps, motors, etc.

- Compact low power replacement for:

- Relays, fuses and discrete circuits

# **Summary Specifications**

| Parameter                                       | Symbol               | Rating    |

|-------------------------------------------------|----------------------|-----------|

| Operating Voltage                               | Vs                   | 5V to 28V |

| Maximum Supply Voltage                          | Vs(LD)               | 41V       |

| Maximum ON Resistance, T <sub>J</sub> = +150°C  | R <sub>DS(ON)</sub>  | 400mΩ     |

| Nominal Load Current                            | I <sub>L</sub> (NOM) | 1.5A      |

| Typical Current Sense Ratio                     | Kılıs                | 300       |

| Minimum Current Limitation                      | I <sub>L5(SC)</sub>  | 6A        |

| Maximum Standby Current, T <sub>J</sub> = +25°C | I <sub>S(OFF)</sub>  | 0.5µA     |

#### Miscellaneous

- Lead-Free Finish; RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- An automotive-compliant part is available under separate datasheet (<u>ZXMS81200SPQ</u>)

Notes:

- 1. EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. All applicable RoHS exemptions applied.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

ZXMS81200SP Document number: DS46001 Rev. 1 - 2

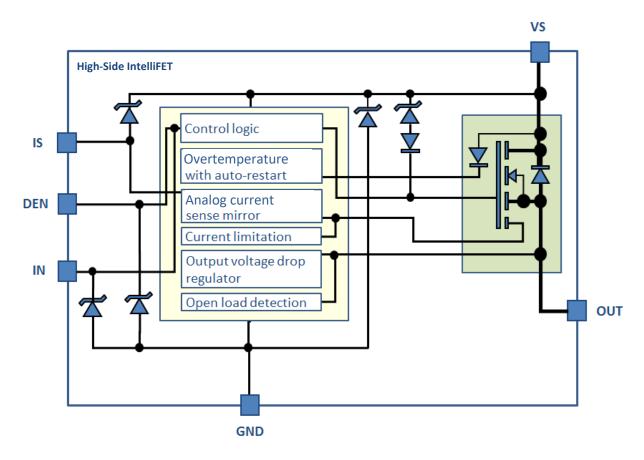

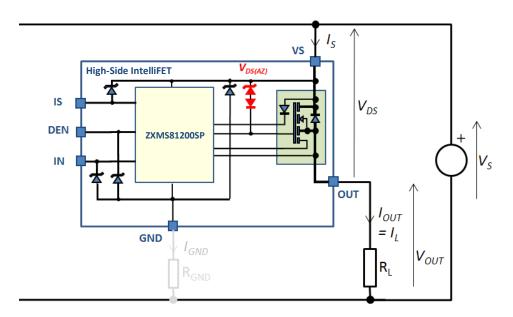

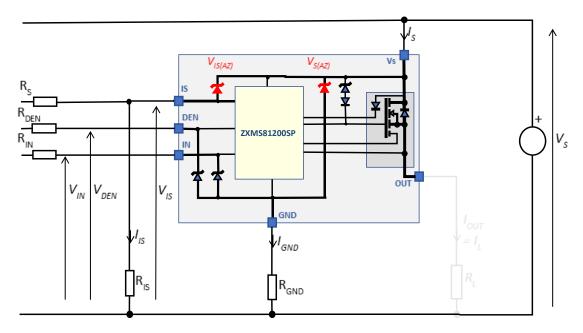

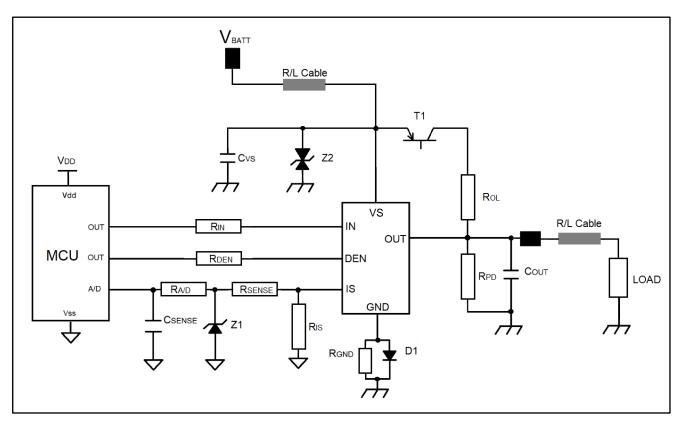

# **Typical Applications Circuit**

Figure 1. Typical Application Configuration

R<sub>GND</sub>, R<sub>IN</sub>, R<sub>DEN</sub> and R<sub>S</sub> are optional. They may be replaced by shorts depending on the application. Non-zero resistors may be used to:

- Reduce peak currents during supply voltage transients that exceed the ±Vs internal clamp voltages

- Typically transients exceeding 41V or may activate the internal clamps

- Protect the customer's application from high currents during transients exceeding 41V

- Keep within rated current during reverse battery, recommended is  $R_S = R_{DEN} = R_{IN} = 4.7 k\Omega$ ,  $R_{GND} = 150\Omega$

- Ensure that the device is off when there is loss of ground connection to the device or module

### **Pin Description**

| Pin Number | Pin Name | Function and Description                                                                                                                                                |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | GND      | Ground or negative supply                                                                                                                                               |  |

| 2          | IN       | Input, activates the output                                                                                                                                             |  |

| 3          | DEN      | Diagnostic enable, allows common connection of the IS pin with multiple devices                                                                                         |  |

| 4          | IS       | Diagnostic output, provides an analog sense current proportional to the load current under normal operation, or a defined current under overload or shutdown conditions |  |

| 5          | NC       | Not connected                                                                                                                                                           |  |

| 6, 7, 8    | OUT      | Output to the load, must be connected together                                                                                                                          |  |

| EP         | VS       | Voltage supply or battery positive                                                                                                                                      |  |

Table 1. Pin Description

# **Functional Block Diagram**

Figure 2. Functional Block Diagram of ZXMS81200SP

### Absolute Maximum Ratings (Notes 4, 5) (@TJ = +25°C, unless otherwise specified.)

|                       | <b>.</b> .                                           | Ra    | tings        |      | 0 11/1                                                                                |  |

|-----------------------|------------------------------------------------------|-------|--------------|------|---------------------------------------------------------------------------------------|--|

| Symbol                | Parameter                                            | Min   | Max          | Unit | Conditions                                                                            |  |

| Supply Voltag         | ge                                                   |       | •            | •    |                                                                                       |  |

| Vs                    | Supply voltage                                       | -0.3  | 28           | V    | _                                                                                     |  |

| V <sub>S(REV)</sub>   | Reverse supply voltage                               | 0     | 16           | V    | $R_L \ge 25\Omega$ , $R_{GND} = 150\Omega$<br>$T_{amb} = +25^{\circ}C$ , $t < 2$ mins |  |

| Vs(sc)                | Supply voltage for short-circuit protection (Note 6) | 0     | 24           | V    | _                                                                                     |  |

| V <sub>S(LD)</sub>    | Supply voltage for load-dump protection (ISO 7637)   |       | 41           | V    | $R_{IN} = 2\Omega$ , $R_L = 25\Omega$                                                 |  |

| Interface Pins        | 3                                                    |       |              |      |                                                                                       |  |

| Mari                  | INI nin voltogo                                      | -0.3  | 6            | V    | _                                                                                     |  |

| Vin                   | IN pin voltage                                       | _     | 7            | V    | t < 2 mins                                                                            |  |

| I <sub>IN</sub>       | Current in IN pin                                    | -2    | 2            | mA   | _                                                                                     |  |

| V                     | DEM nin veltage                                      | -0.3  | 6            | V    | _                                                                                     |  |

| VDEN                  | DEN pin voltage                                      | _     | 7            | V    | t < 2 mins                                                                            |  |

| IDEN                  | Current in DEN pin                                   | -2    | 2            | mA   | _                                                                                     |  |

| V <sub>IS</sub>       | IS pin voltage                                       | -0.3  | Vs           | V    | _                                                                                     |  |

| lıs                   | Current in IS pin                                    | -25   | 50           | mA   | _                                                                                     |  |

| Output Stage          |                                                      |       |              |      |                                                                                       |  |

| IL                    | Load current (Note 7)                                | _     | Self-limited | Α    | _                                                                                     |  |

| Ртот                  | Power dissipation                                    | _     | 1.6          | W    | T <sub>amb</sub> = +85°C, T <sub>J</sub> < +150°C                                     |  |

| Eas                   | Energy dissipation (single pulse)                    | _     | 40           | mJ   | Vs = 13.5V, I <sub>L</sub> = 1A<br>T <sub>J</sub> = +150°C                            |  |

| V <sub>DS</sub>       | VS to OUT pin voltage                                | _     | 41           | V    | _                                                                                     |  |

| Nrsc                  | Repetitive short-circuit capability (Note 8)         |       | 100          | kcyc | ton = 300ms                                                                           |  |

| Current               |                                                      |       |              |      |                                                                                       |  |

| lava                  | Current in GND pin                                   | -10   | 10           | mA   | _                                                                                     |  |

| I <sub>GND</sub>      | Current in GND pin                                   | -150  | 20           | mA   | t < 2 mins                                                                            |  |

| Temperature           |                                                      |       |              |      |                                                                                       |  |

| TJ                    | Junction temperature                                 | -40   | +150         | °C   | _                                                                                     |  |

| Tstg                  | Storage temperature                                  | -55   | +150         | °C   | _                                                                                     |  |

| Electrostatic         | Discharge                                            |       |              |      |                                                                                       |  |

| \/=== ###             | ESD capability HBM (all pins)                        | -2    | 2            | kV   | EIA/IESD 22 A 114B                                                                    |  |

| Vesd(HBM)             | ESD capability HBM OUT to GND and Vs shorted         | -4    | 4            | kV   | - EIA/JESD 22-A 114B                                                                  |  |

| V <sub>ESD(CDM)</sub> | ESD capability CDM                                   | -0.75 | 0.75         | kV   | AEC-Q100-011                                                                          |  |

Notes:

<sup>4.</sup> Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings for extended periods can affect device reliability.

<sup>5.</sup> Not subject to production test, guaranteed by design.

<sup>6.</sup> Short-circuit protection is outside normal operation and is limited to single pulse and allowed combinations of resistance and inductance.

<sup>7.</sup> Current limit is a protection feature and operation in current limitation, e.g. with short-circuit loads, is outside the normal operation range.

<sup>8.</sup> Repetitive short-circuit protection characterisation also carried out according to AEC-Q100-012 at 14V.

## **Package Thermal Data**

| Symbol            | Parameter                                                           |  | Тур | Max | Unit  |

|-------------------|---------------------------------------------------------------------|--|-----|-----|-------|

| R <sub>θ</sub> JC | Thermal resistance, junction-to-case (Note 5)                       |  | 5.2 |     | °C//W |

| R <sub>θ</sub> ЈА | Thermal resistance, junction-to-ambient mounted on PCB (Notes 5, 9) |  | 42  | _   | °C//W |

Note:

## **Recommended Operating Conditions**

| Symbol              | Parameter                            | Min | Max | Unit |

|---------------------|--------------------------------------|-----|-----|------|

| V <sub>S(NOM)</sub> | Nominal operating voltage (Note 10)  | 8   | 18  | V    |

| Vs(op)              | Extended operating voltage (Note 11) | 5   | 28  | V    |

Notes:

- 10. For normal function and protection features.

- 11. Operation across an extended range is possible but is load dependant device may have reduced protection against faulty (overload or short-circuit) loads

## **Operational Electrical Characteristics**

(Unless otherwise specified: -40°C < T<sub>J</sub> < +150°C; typical values based on T<sub>J</sub> = +25°C)

| Symbol                                        | Parameter                                  | Conditions                                                                                                              | Min  | Тур  | Max | Unit |  |  |

|-----------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|--|--|

| General                                       | General                                    |                                                                                                                         |      |      |     |      |  |  |

| V <sub>S(OP)</sub> Extended operating voltage |                                            | V <sub>IN</sub> = 4.5V, V <sub>DS</sub> < 0.5V                                                                          | 5    | 13.5 | 28  | V    |  |  |

| V <sub>S(OP_MIN)</sub>                        | Undervoltage restart                       | $V_{IN} = 4.5V$ , $R_L = 25\Omega$                                                                                      | 3.8  | 4.2  | 5   | V    |  |  |

| Vs(uv)                                        | Undervoltage shutdown                      | $V_{IN} = 4.5V$ , $V_{DEN} = 0V$<br>$R_{L} = 25\Omega$                                                                  | 3    | 3.3  | 4.1 | V    |  |  |

| Vs(uv_Hys)                                    | Undervoltage hysteresis — — —              |                                                                                                                         | 0.85 | _    | V   |      |  |  |

| IGND                                          | Operating current                          | VIN = VDEN = 5.5V, Vs = 18V<br>Device in RDS(ON)                                                                        | _    | 2    | 6   | mA   |  |  |

| 1                                             | Standby ourrant                            | $V_{IN}$ and $V_{DEN}$ floating<br>$V_{OUT} = 0V$ , $V_{S} = 18V$<br>$T_{J} \le +85^{\circ}C$                           | _    | 0.1  | 0.5 | μA   |  |  |

| Is(off)                                       | Standby current                            | V <sub>IN</sub> and V <sub>DEN</sub> floating<br>V <sub>OUT</sub> = 0V, V <sub>S</sub> = 18V<br>T <sub>J</sub> = +150°C | _    | 3.5  | 20  | μΑ   |  |  |

| Is(off_den)                                   | Standby current with diagnostic pin active | V <sub>IN</sub> floating, V <sub>OUT</sub> = 0V<br>V <sub>S</sub> = 18V, V <sub>DEN</sub> = 5.5V                        | _    | 1    | _   | mA   |  |  |

<sup>9.</sup> Device mounted on vertical PCB, 2" x 2" x 1.6mm, FR4 with 2oz copper for all connections.

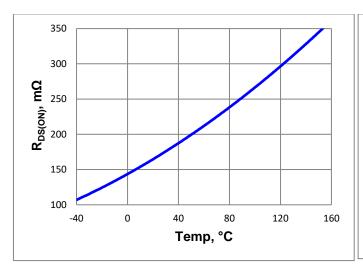

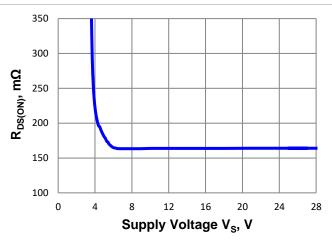

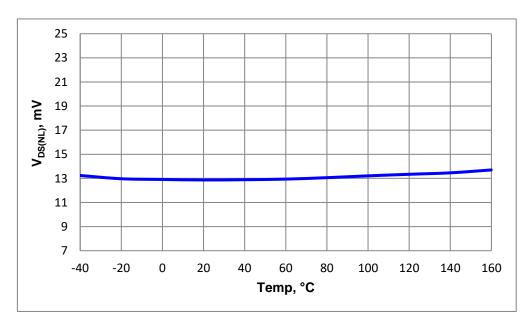

## **Output ON-State Characteristics**

The ON-state resistance R<sub>DS(ON)</sub> depends on the supply voltage V<sub>S</sub> and junction temperature T<sub>J</sub>.

Figure 3. Typical R<sub>DS</sub> ON-State Resistance

At low load current  $I_L$ , the MOSFET gate drive is reduced to maintain a near constant output voltage drop  $V_{DS(NL)}$ . This limits the effect of internal op-amp offset voltage, to maintain useful  $K_{ILIS}$  ratio accuracy even at very low  $I_L$ .

Figure 4. Output Voltage Drop Regulation

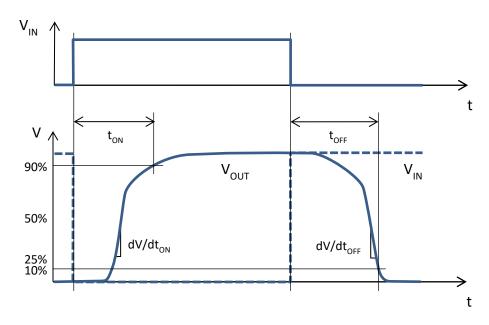

### **Resistive Load Switching**

The power MOSFET turn-ON and turn-OFF processes are determined by the device itself, with rates suitable for EMC compatibility.

Figure 5. Switching a Resistive Load

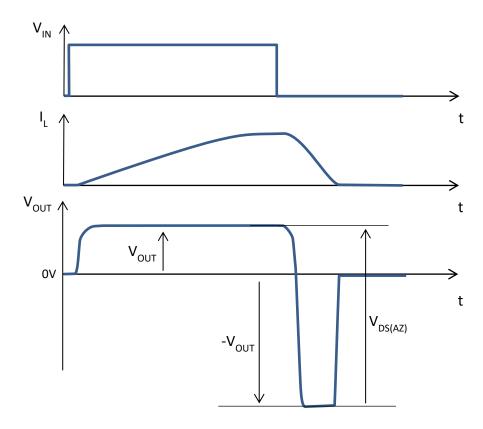

## **Output Inductive Load Clamp**

To de-energise inductive loads the OUT terminal must be allowed to swing below ground (VouT rings negative) during the OFF state.

Figure 6. Output Clamp

# Output Inductive Load Clamp (continued)

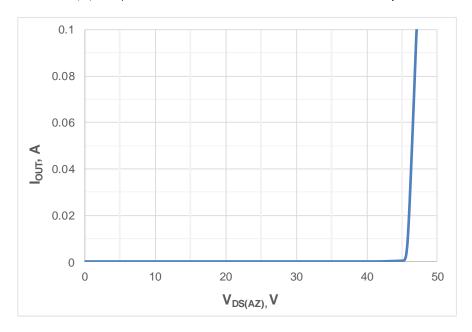

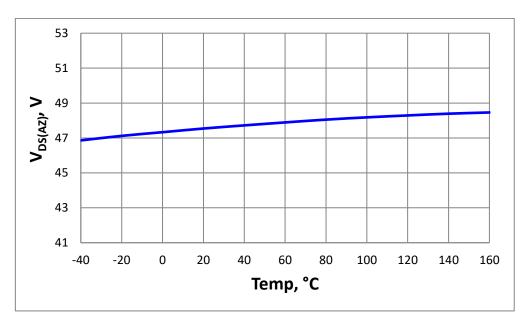

A low-impedance active voltage clamp uses the MOSFET channel to limit the maximum voltage across the MOSFET drain-source terminals, limiting the swing of OUT below  $V_S$  to safe  $V_{DS(AZ)}$ . This prevents avalanche of the MOSFET or associated circuitry.

Figure 7. Typical V<sub>DS</sub> Clamp Characteristic

Figure 8. Switching an Inductive Load

### **Maximum Load Inductance**

Stored inductive load ring-OFF energy is dissipated in the MOSFET during switching and load ring-OFF clamping. Additional energy is also supplied to the system by the Vs supply until the load current I<sub>L</sub> reaches zero. This causes a temporary rise in MOSFET temperature after turn-OFF begins. The temperature reached depends on the starting temperature, thermal environment, load current I<sub>L</sub>, load inductance L<sub>L</sub>, load resistance R<sub>L</sub> and supply voltage Vs.

### **Inverse Current Capability**

In the ON-state the device will remain on if the output current becomes inverse until or unless the inverse current becomes high enough to create a -V<sub>DS</sub> approaching body diode conduction. During inverse current conduction, I<sub>L(INV)</sub>, the IS sense output will be zero. If body diode conduction occurs all functions are disabled or unspecified until the inverse current becomes very small.

If inverse current is present in the OFF state body diode conduction occurs and all functions are disabled or unspecified. When inverse current is removed or becomes very small then turn-ON and normal function become possible.

### **Power Stage Electrical Characteristics**

(Unless otherwise specified: 8V < Vs < 18V, -40°C < T<sub>J</sub> < +150°C; typical values based on Vs = 13.5V, T<sub>J</sub> = +25°C.)

| Symbol               | Parameter Conditions                          |                                                                        | Min | Тур  | Max | Unit |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------|-----|------|-----|------|

| Output Charac        | cteristics                                    | <u> </u>                                                               | •   | •    | •   |      |

| Rds(on)              | ON-state resistance                           | V <sub>IN</sub> = 4.5V, I <sub>L</sub> = 1A<br>T <sub>J</sub> = +150°C | _   | 360  | 400 | mΩ   |

| ()                   |                                               | V <sub>IN</sub> = 4.5V, I <sub>L</sub> = 1A                            | _   | 200  | _   | mΩ   |

| IL(NOM)              | Nominal load current (Note 12)                | T <sub>amb</sub> = +85°C, T <sub>J</sub> < +150°C                      | _   | 1.5  | _   | Α    |

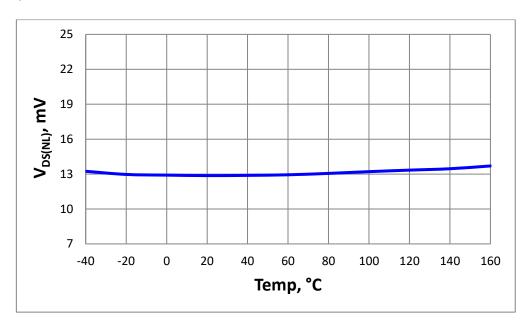

| V <sub>DS(NL)</sub>  | Voltage drop regulation at low I <sub>L</sub> | I <sub>L</sub> = 25mA                                                  | _   | 12   | 25  | mV   |

| V <sub>DS(AZ)</sub>  | Output clamp voltage                          | I <sub>L</sub> = 20mA                                                  | 41  | 47   | 53  | V    |

|                      |                                               | V <sub>IN</sub> floating, V <sub>OUT</sub> = 0V                        | _   | 0.1  | 0.5 | μA   |

| I <sub>L</sub> (OFF) | Output leakage current                        | VIN floating, Vout = 0V<br>T <sub>amb</sub> = +150°C                   | _ 3 | 10   | μΑ  |      |

| I <sub>L(INV)</sub>  | Inverse output current (Note 13)              | V <sub>S</sub> < V <sub>OUT</sub>                                      | _   | 1    | _   | Α    |

| Timings              |                                               |                                                                        |     |      |     |      |

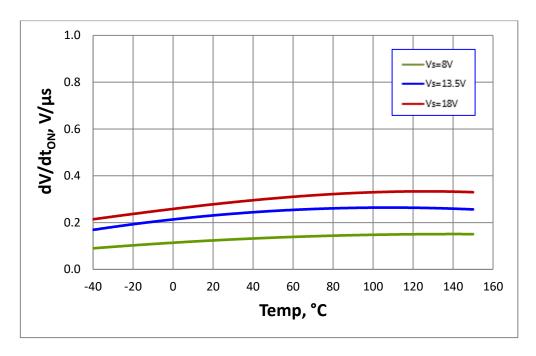

| dV/dton              | Slew rate ON, 30% to 70% Vs                   |                                                                        | 0.1 | 0.2  | 1.0 | V/µs |

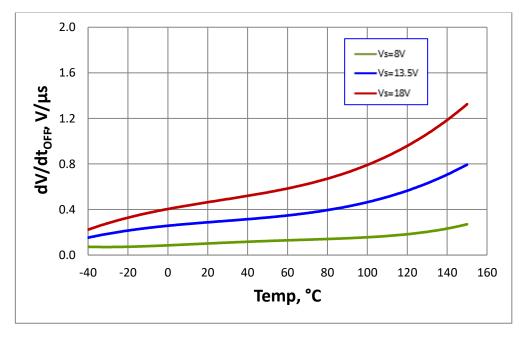

| dV/dtoff             | Slew rate OFF, 70% to 30% Vs                  |                                                                        | 0.2 | 0.3  | 1.0 | V/µs |

| ton                  | Turn-ON time to 90% V <sub>S</sub>            | D 050 V 40 5V                                                          | 20  | 110  | 160 | μs   |

| toff                 | Turn-OFF time to 10% Vs                       | $R_L = 25\Omega$ , $V_S = 13.5V$                                       | 20  | 150  | 260 | μs   |

| ton(DELAY)           | Turn-ON delay to 10% Vs                       |                                                                        | 10  | 30   | 70  | μs   |

| toff(DELAY)          | Turn-OFF delay to 90% V <sub>S</sub>          |                                                                        | 10  | 80   | 190 | μs   |

| Eon                  | Switch ON energy                              | $R_L = 25\Omega, V_S = 18V$<br>$V_{OUT} = 90\% V_S$                    | _   | 0.19 | _   | mJ   |

| Eoff                 | Switch OFF energy                             | $R_L = 25\Omega, V_S = 18V$<br>$V_{OUT} = 10\% V_S$                    |     | 0.16 | _   | mJ   |

Notes: 12. Device mounted on vertical 50mm x 50mm x 1.5mm FR4 single-sided PCB with 6cm² 2oz copper in free air.

13. ON-state reverse conduction, functional test only.

### **Protection Features**

#### **Loss of Ground Protection**

The device will turn off in the case that the ground pin connection is lost and the load remains connected. It is recommended to use high ohmic input resistors in the interface pins to ensure that the device is turned off by limiting the current in the paths from the ground pin, through the input and diagnostic enable ESD diodes, to the external driving circuits.

#### **Undervoltage Protection**

The device will not turn on if the Vs supply voltage is below the minimum operating voltage  $V_{S(OP\_MIN)}$  where protection functions may not be operational. If the device is already on then the supply voltage has to drop to below the under voltage threshold  $V_{S(UV)}$  to turn the output off. Figure 9 shows the undervoltage mechanism.

Figure 9. Undervoltage Behavior

### **Protection Features (continued)**

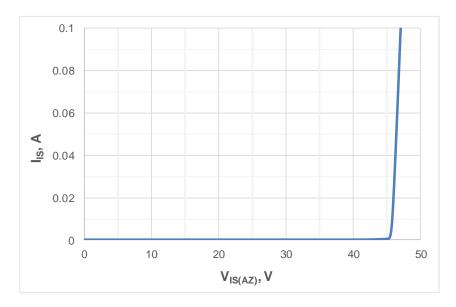

#### **Overvoltage Protection**

Figure 10. Overvoltage Clamping Circuit

The GND pin has an active protection clamp, operating much as a low noise high voltage Zener device, to protect it from overvoltage for high Vs transients. During Vs transient overvoltage the voltage is clamped and the excess voltage, Vs-Vs(AZ), is applied across the ground resistor RgND raising the potential on the GND pin. Additional high ohmic series resistors may be needed to prevent high VIN and VDEN being applied directly to the driving circuits.

The IS pin also has an active protection clamp and during Vs transient overvoltage the voltage is clamped and excess voltage, Vs-V<sub>IS(AZ)</sub>, is applied across the sense resistor R<sub>IS</sub>. An additional high ohmic series resistor may be needed in the application to prevent high V<sub>IS</sub> being applied directly to the application monitoring circuit.

Figure 11. Typical V<sub>S</sub>-V<sub>IS</sub> Clamp Characteristic

### **Protection Features (continued)**

Also during Vs overvoltage transient the voltage Vs-OUT is clamped and the excess voltage, Vs-V<sub>DS(AZ)</sub>, is applied across the load R<sub>L</sub>. Vs-OUT is the same clamp described under the earlier section <u>Output Inductive Load Clamp</u>.

#### **Reverse Battery Protection**

During reverse battery the output body diode is conducting current limited by the load itself resulting in power dissipation and the current in the ground and logic inputs has to be limited by external resistor components. No operating functions are available in this condition.

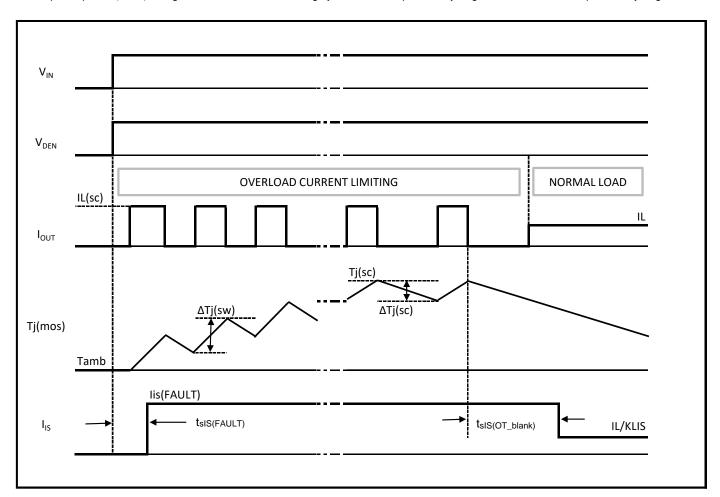

#### **Overload Protection**

During overload the output current is limited to a value depending on the  $V_{DS}$  voltage resulting in high dissipation in the output power stage. Sustained operation in this mode will raise the internal junction temperature until dynamic or absolute overtemperature protection cycling begins. There is a dynamic ( $\Delta T_{J(SW)}$ ) and an absolute ( $T_{J(SC)}$ ) temperature sensor. Figure 12 gives a sketch of overload protection.

If the temperature rise of the power stage versus the cooler control area exceeds  $\Delta T_{J(SW)}$  then the device will be turned off until the rise falls to a reset level. Each cycle causes the absolute temperature to increase a little.

If the absolute temperature reaches  $T_{J(SC)}$  then the device will be turned off until the absolute temperature falls by  $\Delta T_{J(SC)}$ . The device will continue to cycle to  $T_{J(SC)}$  as long as the fault condition remains.

The IS pin outputs I<sub>IS(FAULT)</sub> during load current limitation, during dynamic overtemperature cycling, and absolute overtemperature cycling.

Figure 12. Overload Protection Diagram

### **Protection Electrical Characteristics**

(Unless otherwise specified:  $8V < V_S < 18V$ ,  $-40^{\circ}C < T_J < +150^{\circ}C$ ; typical values based on  $V_S = 13.5V$ ,  $T_J = +25^{\circ}C$ )

| Symbol               | Parameter                                             | Min                                           | Тур  | Max  | Unit |    |

|----------------------|-------------------------------------------------------|-----------------------------------------------|------|------|------|----|

| Loss of Gro          | ound Protection                                       |                                               |      |      |      |    |

| IOUT(GND)            | Output leakage current (Note 14)                      | Vs = 28V<br>GND disconnected                  | _    | 0.1  | _    | mA |

| Reverse Ba           | ttery Protection                                      |                                               |      |      |      |    |

| VDS(REV)             | Reverse output voltage (Note 15)                      | I <sub>L</sub> = -1A; T <sub>J</sub> = +150°C | 0.2  | 0.65 | 0.7  | V  |

| Overvoltag           | Overvoltage Protection                                |                                               |      |      |      |    |

| Vs(AZ)               | Vs to GND clamping                                    | Is = 5mA                                      | 41   | 47   | 53   | V  |

| Overload P           | rotection                                             |                                               |      |      |      |    |

| I <sub>L5(SC)</sub>  | Load current limit                                    | V <sub>DS</sub> = 5V                          | 6    | 9    | 12   | Α  |

| I <sub>L</sub> (RMS) | Load current during overtemperature cycling (Note 14) | $R_{SHORT} = 0.1\Omega$<br>LSHORT = 5 $\mu$ H | _    | 2    | _    | Α  |

| $\Delta T_{J(SW)}$   | Dynamic temperature rise during cycling (Note 16)     | _                                             | _    | 80   | _    | К  |

| T <sub>J</sub> (SC)  | Thermal shutdown temperature (Note 17)                |                                               | +150 | +170 | +200 | °C |

| ΔT <sub>J</sub> (SC) | Thermal hysteresis (Note 17)                          | _                                             | _    | 20   | _    | K  |

Notes:

- 14. Not subject to production test, guaranteed by design.

- 15. During reverse battery the body-drain diode will conduct with voltage drop  $V_{DS(REV)}$ .

- 16. Functional test only.

- 17. Functional test only at  $T_J = +150$ °C.

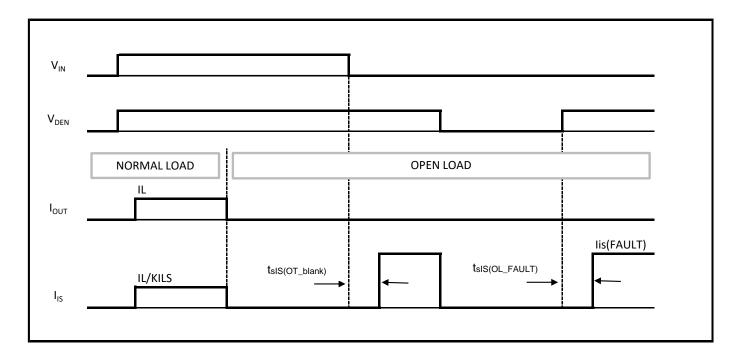

### **Diagnostic Functionality - Detailed Description**

In normal operation the IS pin outputs a small analog sense current proportional to the main OUT current flowing in the power MOSFET. In the case where it is disabled by the DEN pin it becomes high impedance. During overload/current limit operation/overtemperature/high temperature gradient or open load in the OFF state, the IS pin outputs a defined current I<sub>IS(FAULT)</sub> greater than normal sense currents for normal loads. During ON-state operation with open load, normal OFF-state, or OFF-state with inductive load ring-off current still flowing, the IS current is approximately zero.

| Operating Condition                 | V <sub>IN</sub> | V <sub>DEN</sub> | V <sub>OUT</sub> | IS Output Current, I <sub>IS</sub> |

|-------------------------------------|-----------------|------------------|------------------|------------------------------------|

| Normal operation                    | L               | H                | Z                | Z                                  |

|                                     | H               | H                | H                | = IL / KILIS                       |

| Current limiting                    | Н               | Н                | Н                | lis(fault)                         |

| Short circuit OUT to GND            | L               | H                | L                | Z                                  |

|                                     | H               | H                | L                | IIS(FAULT)                         |

| Overtemperature                     | L               | H                | Z                | Z                                  |

|                                     | H               | H                | Z                | I <sub>IS(FAULT)</sub>             |

| Short circuit OUT to V <sub>S</sub> | L<br>H          | H<br>H           | H<br>H           | IIS(FAULT) < IL / KILIS (Note 18)  |

| Open load                           | L               | H                | < VOL(OFF)       | Z                                  |

|                                     | L               | H                | > VOL(OFF)       | I <sub>IS(FAULT)</sub>             |

|                                     | H               | H                | H                | < I <sub>IS(OL)</sub> (Note 19)    |

| Inverse load current                | L               | H                | H                | lis(fault)                         |

|                                     | H               | H                | H                | lis(ol)                            |

| All                                 | Х               | L                | Х                | Z                                  |

Table 2. Operational Truth Table (Note 20)

Notes: 18. A low resistance short between OUT and V<sub>S</sub> will reduce the output current, I<sub>L</sub> and therefore reduce the analog sense current, I<sub>IS</sub>.

- 19. With external pullup resistor.

- 20. H = high level; L = low level; Z = high impedance, voltage depends on external circuit; X = don't care.

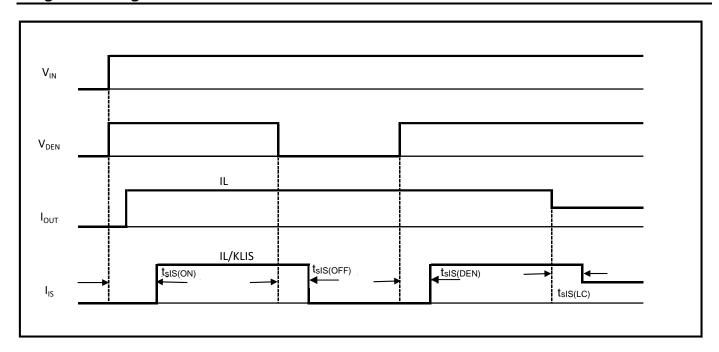

# **Diagnostic Diagrams**

Figure 13. IS Signal Timing Diagram

Figure 14. Open-Load Timing Diagram

Diagnostic Electrical Characteristics (Unless otherwise specified:  $8V < V_S < 18V$ ,  $-40^{\circ}C < T_J < +150^{\circ}C$ ; typical values based on  $V_S = 13.5V$ ,  $T_J = +25^{\circ}C$ )

| Symbol                         | Parameter                                                                                                                                      | Conditions                                                                                                                               | Min  | Тур | Max  | Unit |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Open-Load                      | I Detection                                                                                                                                    |                                                                                                                                          |      |     |      |      |

| V <sub>DS(OL)</sub>            | Open-load OFF state detection voltage                                                                                                          | V <sub>IN</sub> = 0V, V <sub>DEN</sub> = 4.5V                                                                                            | 3.5  | _   | 6    | V    |

| IL(OL)                         | Open-load ON state detection current                                                                                                           | $V_{IN} = V_{DEN} = 4.5V$<br>$I_{IS(OL)} = 33\mu A$                                                                                      | 5    | _   | 15   | mA   |

| Current Ser                    | nse Pin                                                                                                                                        |                                                                                                                                          |      |     |      |      |

| lis(DIS)                       | Current sense leakage current                                                                                                                  | V <sub>IN</sub> = 4.5V, V <sub>DEN</sub> = 0V<br>I <sub>L</sub> = 1A                                                                     | _    | _   | 1    | μA   |

| V <sub>IS(SAT)</sub>           | VS to IS saturation voltage                                                                                                                    | V <sub>IN</sub> = 0V, V <sub>DEN</sub> = 4.5V<br>I <sub>IS</sub> = 6mA, V <sub>OUT</sub> = V <sub>S</sub> > 10V                          | _    | _   | 3    | V    |

| I <sub>IS(FAULT)</sub>         | Current sense under fault conditions                                                                                                           | V <sub>IN</sub> = V <sub>IS</sub> = 0V, V <sub>DEN</sub> = 4.5V<br>V <sub>OUT</sub> = V <sub>S</sub> > 10V                               | 6    | 15  | 35   | mA   |

| VIS(AZ)                        | VS to IS clamp voltage                                                                                                                         | lis = 5mA                                                                                                                                | 41   | 47  | 53   | V    |

| Load Curre                     | nt Sense                                                                                                                                       |                                                                                                                                          |      |     |      |      |

| K <sub>ILIS0</sub>             | Sense current ratio I <sub>L</sub> = 10mA                                                                                                      |                                                                                                                                          | -40% | 320 | +40% | _    |

| KILIS1                         | Sense current ratio I∟ = 0.05A                                                                                                                 |                                                                                                                                          | -35% | 320 | +35% | _    |

| K <sub>ILIS2</sub>             | Sense current ratio I <sub>L</sub> = 0.2A                                                                                                      |                                                                                                                                          | -12% | 320 | +12% | _    |

| K <sub>ILIS3</sub>             | Sense current ratio I <sub>L</sub> = 0.5A                                                                                                      | VIN = VDEN = 4.5V                                                                                                                        | -9%  | 300 | +9%  | _    |

| K <sub>ILIS4</sub>             | Sense current ratio I <sub>L</sub> = 1A                                                                                                        |                                                                                                                                          | -6%  | 300 | +6%  | _    |

| ΔKILIS                         | Sense current ratio variation I <sub>L</sub> = 0.5A versus I <sub>L</sub> = 0.2A                                                               |                                                                                                                                          | -9%  | 0   | +9%  | _    |

| Diagnostic                     | Timings                                                                                                                                        |                                                                                                                                          |      |     |      |      |

| tsIS(ON)                       | Current sense settling time to 90% I <sub>IS</sub> after IN and DEN high                                                                       | $V_S = 13.5V$ , $V_{IN} = V_{DEN} = 4.5V$<br>$I_L = 0.5A$ , $R_{IS} = 1.2k\Omega$                                                        | _    | _   | 150  | μs   |

| tsIS(DEN)                      | Current sense settling time to 90% lis after DEN high                                                                                          | $V_S = 13.5V, V_{IN} = 4.5V$<br>$I_L = 0.5A, R_{IS} = 1.2k\Omega$                                                                        | _    | _   | 20   | μs   |

| tsIS(LC)                       | Current sense settling time to 90% lis after load current change                                                                               | $V_S = 13.5V$ , $V_{IN} = V_{DEN} = 4.5V$<br>$I_L = 0.2A$ to 2A, $R_{IS} = 1.2k\Omega$                                                   | _    | _   | 15   | μs   |

| t <sub>sIS(OL_</sub><br>FAULT) | Diagnostic fault current settling time to 90%  IIS(FAULT) after DEN high with OFF state open- load condition                                   | $V_{IN} = 0V$ , $V_{OUT} = V_S = 13.5V$<br>$R_{IS} = 1.2k\Omega$                                                                         | _    | _   | 50   | μs   |

| tsis(FAULT)                    | Diagnostic fault current settling time to 90%  IIS(FAULT) after IN and DEN high with overload condition                                        | $V_{DS} = 5V$ , $R_{IS} = 1.2k\Omega$                                                                                                    | _    | _   | 150  | μs   |

| tsIS(OT_<br>blank)             | Diagnostic fault current off delay time to 90%  I <sub>IS(FAULT)</sub> after overtemperature condition returning to normal operation (Note 21) | $\begin{aligned} &\text{V}_{\text{IN}} = \text{V}_{\text{DEN}} = 4.5\text{V} \\ &\text{R}_{\text{IS}} = 1.2\text{k}\Omega \end{aligned}$ | _    | 150 | _    | μs   |

| t <sub>sIS(OFF)</sub>          | Current sense fall time to < 50% lis after DEN low                                                                                             | $V_{IN} = 4.5V$ , $I_L = 0.5A$<br>$R_{IS} = 1.2k\Omega$                                                                                  | _    | _   | 20   | μs   |

21. Not subject to production test. Note:

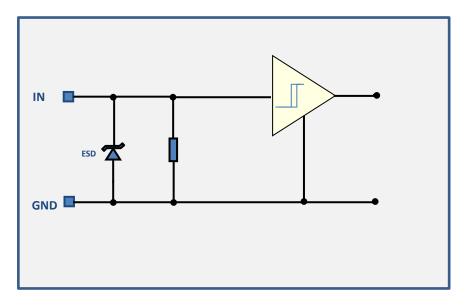

## **Input Pins**

The input circuit is compatible with 3.3V and 5V logic levels. The input diode provides ESD protection. If the pin is left open the internal tie down resistor will keep the output off. A Schmitt trigger provides switching hysteresis to avoid an undefined state if there is a slowly rising or falling voltage on the IN pin. Figure 15 shows the electrical equivalent circuit.

Figure 15. Input Pin Circuitry

The DEN pin has the same circuitry as the IN pin above.

### **Input Electrical Characteristics**

(Unless otherwise specified:  $8V < V_S < 18V$ ,  $-40^{\circ}C < T_J < +150^{\circ}C$ ; typical values based on  $V_S = 13.5V$ ,  $T_J = +25^{\circ}C$ )

| Symbol              | Parameter                | Conditions              |      | Тур  | Max | Unit |

|---------------------|--------------------------|-------------------------|------|------|-----|------|

| IN Pin              |                          |                         |      |      |     |      |

| V <sub>IN(L)</sub>  | Low level input voltage  | _                       | -0.3 | _    | 0.8 | V    |

| V <sub>IN(H)</sub>  | High level input voltage | _                       | 2    | _    | 6   | V    |

| VIN(HYS)            | Input voltage hysteresis | _                       | _    | 0.25 | _   | V    |

| lin(L)              | Low level input current  | V <sub>IN</sub> = 0.8V  | 1    | 3    | 25  | μΑ   |

| I <sub>IN(H)</sub>  | High level input current | V <sub>IN</sub> = 5.5V  | 2    | 8    | 25  | μA   |

| DEN Pin             |                          |                         |      |      |     |      |

| V <sub>DEN(L)</sub> | Low level input voltage  | _                       | -0.3 | _    | 0.8 | V    |

| V <sub>DEN(H)</sub> | High level input voltage | _                       | 2    | _    | 6   | V    |

| VDEN(HYS)           | Input voltage hysteresis | _                       | _    | 0.25 | _   | V    |

| I <sub>DEN(L)</sub> | Low level input current  | V <sub>DEN</sub> = 0.8V | 1    | 3    | 25  | μA   |

| IDEN(H)             | High level input current | V <sub>DEN</sub> = 5.5V | 2    | 8    | 25  | μΑ   |

### **Characterisation – General Product**

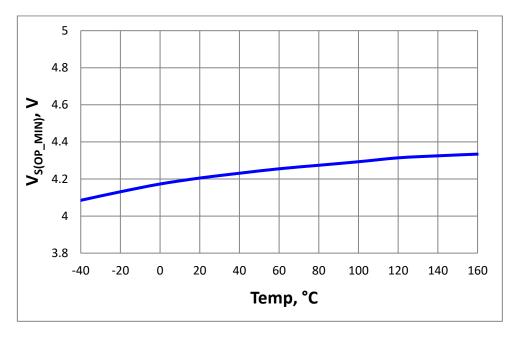

### **Minimum Functional Supply Voltage**

Figure 16. Minimum Functional Supply Voltage  $V_{S(OP\_MIN)} = f(T_J)$

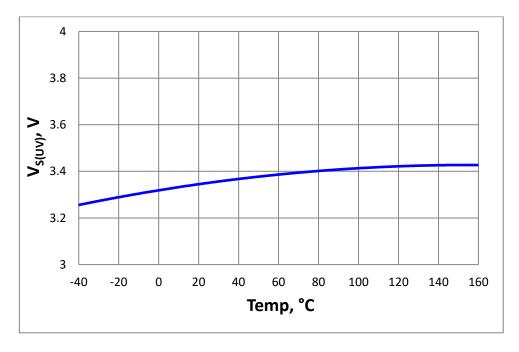

#### **Undervoltage Shutdown**

Figure 17. Undervoltage Shutdown  $V_{S(UV)} = f(T_J)$

# Characterisation - General Product (continued)

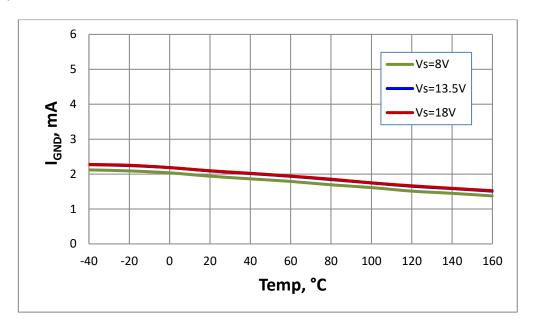

#### **Current Consumption Channel Active**

Figure 18. Current Consumption for Whole Device with Load, Channel Active IGND = f(TJ;VS)

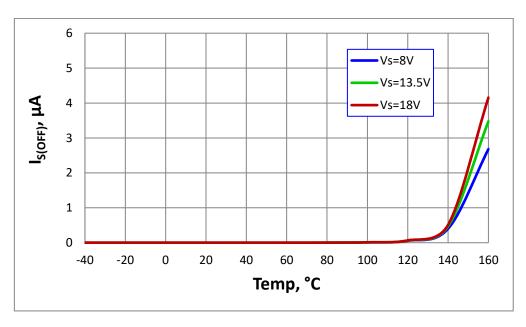

#### Standby Current for Whole Device with Load

Figure 19. Standby Current for Whole Device with Load  $I_{S(OFF)} = f(T_J; V_S)$

## Characterisation - Power Stage

#### **Output Voltage Drop Limitation at Low Load Current**

Figure 20. Output Voltage Drop Limitation at Low Load Current VDS(NL) = f(TJ)

#### **Drain to Source Clamp Voltage**

Figure 21. Drain to Source Clamp Voltage  $V_{DS(AZ)} = f(T_J)$

# Characterisation - Power Stage (continued)

#### Slew Rate at Turn ON

Figure 22. Slew Rate at Turn ON  $dV/dt_{ON} = f(T_J;V_S)$ ,  $R_L = 25\Omega$

### Slew Rate at Turn OFF

Figure 23. Slew Rate at Turn OFF  $dV/dt_{OFF} = f(T_J; V_S)$ ,  $R_L = 25\Omega$

# Characterisation - Power Stage (continued)

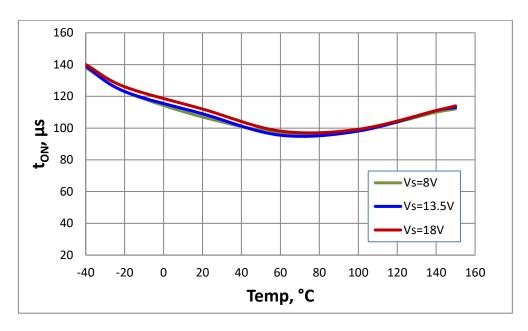

#### **Turn ON Time**

Figure 24. Turn ON ton =  $f(T_J;V_S)$ , RL=  $25\Omega$

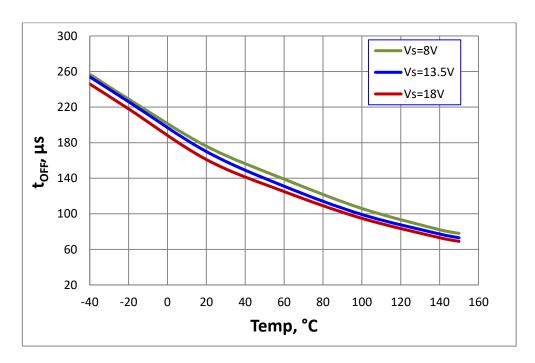

#### **Turn OFF Time**

Figure 25. Turn OFF toff =  $f(T_J; V_S)$ ,  $R_L = 25\Omega$

# Characterisation - Power Stage (continued)

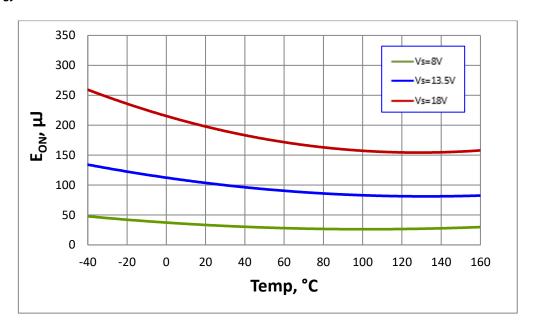

#### **Switch ON Energy**

Figure 26. Switch ON Energy Eon =  $f(T_J; V_S)$ ,  $R_L = 25\Omega$

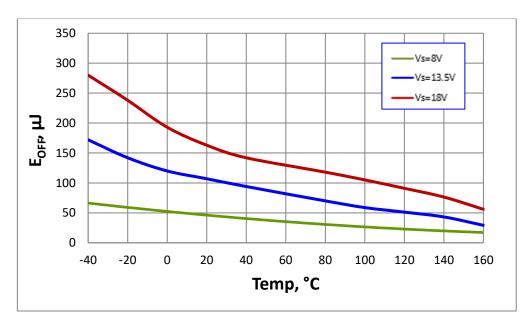

#### **Switch OFF Energy**

Figure 27. Switch OFF Energy E<sub>OFF</sub> =  $f(T_J;V_S)$ ,  $R_L = 25\Omega$

## **Characterisation - Protection**

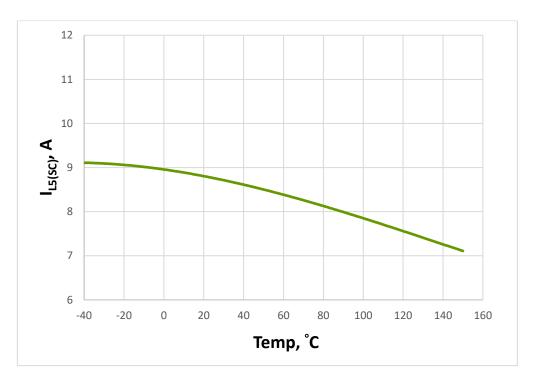

### **Overload Condition**

Figure 28. Overload Condition  $I_{L5(SC)} = f(T_J)$

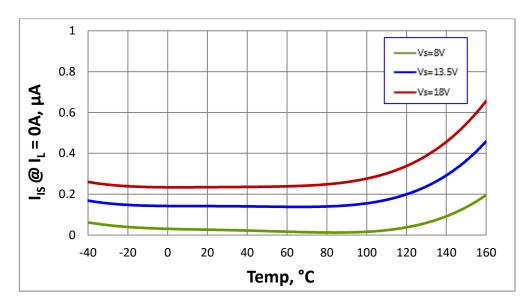

# **Characterisation – Diagnostic Mechanism**

#### **Current Sense at No Load**

Figure 29. Current Sense at No Load IIs = f(TJ;Vs)

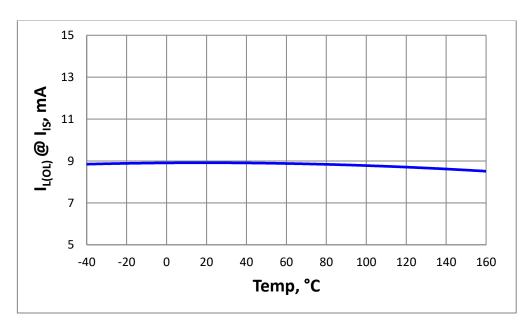

#### Open-Load Detection Threshold in ON State

Figure 30. Open-Load Detection ON State Threshold  $I_{L(OL)} = f(T_J)$

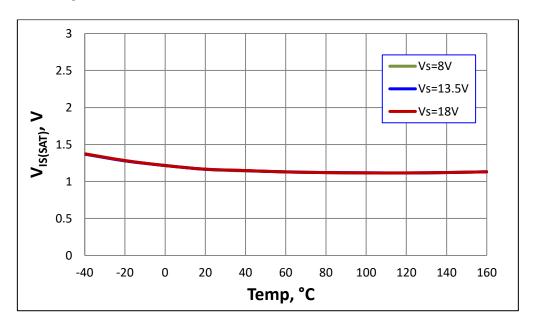

### Characterisation - Diagnostic Mechanism (continued)

#### Sense Signal Maximum Voltage

Figure 31. Sense Signal Maximum Voltage  $V_{IS(SAT)} = f(T_J; V_S)$

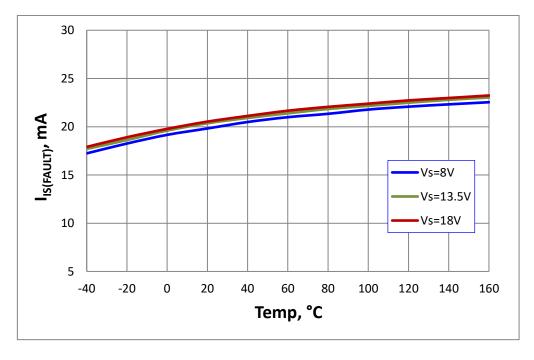

#### **Sense Signal Maximum Current**

Figure 32. Sense Signal Maximum Current in Fault Condition  $Iis(FAULT) = f(T_J;V_S)$

# **Characterisation – Input Pins**

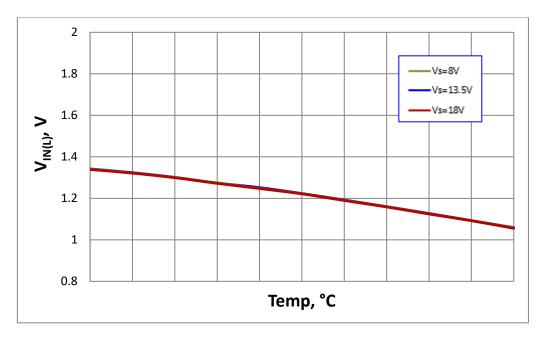

### Input Voltage Threshold ON to OFF

Figure 33. Input Voltage Threshold  $V_{IN(L)} = f(T_J; V_S)$

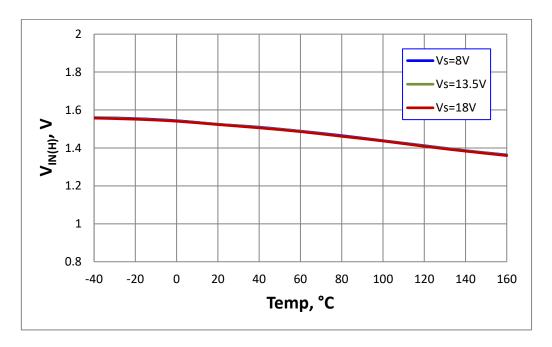

### Input Voltage Threshold OFF to ON

Figure 34. Input Voltage Threshold  $V_{IN(H)} = f(T_J; V_S)$

# Characterisation - Input Pins (continued)

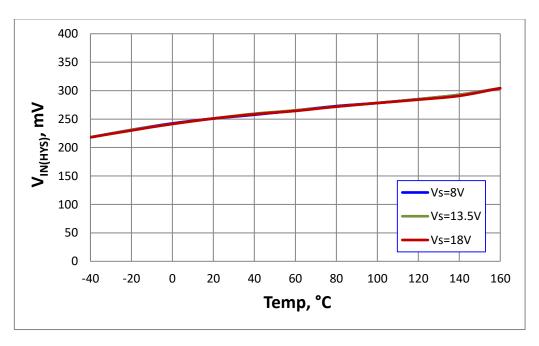

### Input Voltage Hysteresis

Figure 35. Input Voltage Hysteresis  $V_{IN(HYS)} = f(T_J; V_S)$

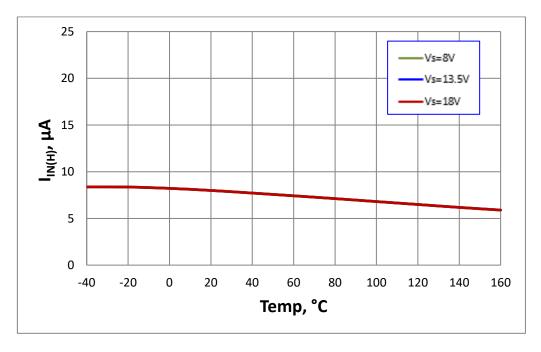

#### Input Current High Level

Figure 36. Input Current High Level  $I_{IN(H)} = f(T_J; V_S)$

## **Application Information** (Note 22)

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 37. Application Diagram

Note: 22. This is a very simplified example of an application circuit. The function must be verified in the real application.

| Reference        | Value           | Purpose                                                                                              |  |

|------------------|-----------------|------------------------------------------------------------------------------------------------------|--|

| Rin              | 4.7kΩ           | Connect to the micro controller for overvoltage, reverse polarity protections                        |  |

| R <sub>DEN</sub> | 4.7kΩ           | Connect to the micro controller for overvoltage, reverse polarity protections                        |  |

| R <sub>PD</sub>  | 47kΩ            | Improve immunity to electromagnetic noise                                                            |  |

| R <sub>IS</sub>  | 1.2kΩ           | Sense resistor                                                                                       |  |

| Rsense           | 4.7kΩ           | Overvoltage, reverse polarity, loss of ground. Value to be tuned with micro controller specification |  |

| RoL              | 1.5kΩ           | For open load in OFF diagnostic                                                                      |  |

| R <sub>A/D</sub> | 4.7kΩ           | Protection for the micro controller during overvoltage, reverse polarity                             |  |

| Rgnd             | 1kΩ             | To keep the device GND at a stable potential during clamping                                         |  |

| D1               | BAS21           | Protection of the device during reverse polarity                                                     |  |

| Z1               | 7V Zener diode  | Protection of the micro controller during overvoltage                                                |  |

| Z2               | 36V Zener diode | Protection of the device during overvoltage                                                          |  |

| T1               | BC 807          | Switch the battery voltage for open load in OFF diagnostic                                           |  |

| Csense           | 100pF           | Sense signal filtering                                                                               |  |

| C <sub>VS</sub>  | 100nF           | Filtering of the voltage spikes on the battery line                                                  |  |

| Соит             | 4.7nF           | Protection of the device during ESD and BCI                                                          |  |

Table 3. Bill of Materials

## Ordering Information (Note 23)

| Part Number    | Package         | Marking   | Reel Size (inches) | Tape Width (mm) | Packing |         |

|----------------|-----------------|-----------|--------------------|-----------------|---------|---------|

|                |                 |           |                    |                 | Qty.    | Carrier |

| ZXMS81200SP-13 | SO-8EP (Type E) | ZXMS81200 | 13                 | 12              | 2500    | Reel    |

Note: 23. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

# **Marking Information**

JH: Manufacturer's Code Marking

ZXMS81200: Product Type Marking Code

YY or YY: Year (ex: 23 = 2023)

WW or WW: Week 01 to 52;

52 represents week 52 and 53

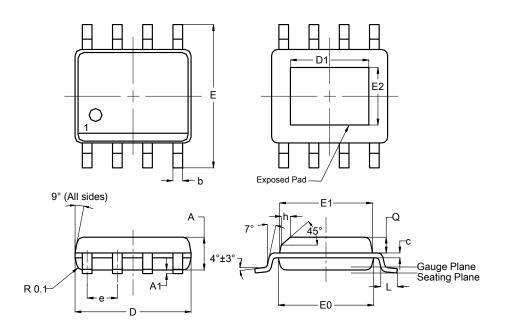

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### SO-8EP (Type E)

| SO-8EP (Type E)      |      |      |      |  |  |

|----------------------|------|------|------|--|--|

| Dim                  | Min  | Max  | Тур  |  |  |

| Α                    | 1.40 | 1.50 | 1.45 |  |  |

| A1                   | 0.00 | 0.13 |      |  |  |

| b                    | 0.30 | 0.50 | 0.40 |  |  |

| С                    | 0.15 | 0.25 | 0.20 |  |  |

| D                    | 4.85 | 4.95 | 4.90 |  |  |

| D1                   | 2.65 | 3.75 | 3.70 |  |  |

| Е                    | 5.90 | 6.10 | 6.00 |  |  |

| E0                   | 3.85 | 3.95 | 3.90 |  |  |

| E1                   | 3.80 | 3.90 | 3.85 |  |  |

| E2                   | 2.05 | 2.15 | 2.10 |  |  |

| е                    | 1    | 1    | 1.27 |  |  |

| h                    |      |      | 0.35 |  |  |

| L                    | 0.62 | 0.82 | 0.72 |  |  |

| ø                    | 0.60 | 0.70 | 0.65 |  |  |

| All Dimensions in mm |      |      |      |  |  |

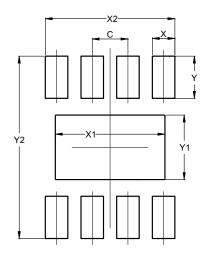

### **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### SO-8EP (Type E)

| Dimensions | Value   |  |  |

|------------|---------|--|--|

| Dimensions | (in mm) |  |  |

| С          | 1.270   |  |  |

| Χ          | 0.802   |  |  |

| X1         | 3.900   |  |  |

| X2         | 4.612   |  |  |

| Υ          | 1.505   |  |  |

| Y1         | 2.300   |  |  |

| Y2         | 6.500   |  |  |

### **Mechanical Data**

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 @3

- Weight: 0.08 grams (Approximate)

#### **IMPORTANT NOTICE**

- 1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<a href="https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/">https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</a>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners.

© 2023 Diodes Incorporated. All Rights Reserved.

www.diodes.com