#### 2.7W STEREO AUDIO POWER AMPLIFIER WITH 4 SELECTABLE GAIN SETUPS AND INPUT MUX

## Description

The AA4006 is a Class AB stereo audio power amplifier with headphone driver, which can deliver 2.7W into  $3\Omega$  speakers with 5.0V power supply and THD+N less than 10%. It is designed specially for notebook PC and portable media player applications.

The AA4006 features stereo full differential input or 2 sets of stereo single-ended audio input. There are 4 different gain settings at BTL mode -6dB, 10dB, 15.6dB and 21.6dB, changed by setting GAIN0, GAIN1 pins. At SE mode, the gain is fixed 4.1dB.

The AA4006 can amplify square waveform beep input signal from BEEP\_IN pin and its' output can always reach BTL terminal, masking all other audio inputs regardless of whether the chip is in shutdown, SE or BTL mode.

The AA4006 is available in TSSOP-24 (EDP) package.

### Features

- Output Power, THD+N=10%: 110mW at SE Mode for 32Ω Headphone 220mW at SE Mode for 16Ω Headphone 1.5W at BTL Mode for 8Ω Speaker 2.3W at BTL Mode for 4Ω Speaker 2.7W at BTL Mode for 3Ω Speaker

- Supply Voltage Range: 4.5V to 5.5V

- 4 Selectable Internal Fixed Gain Setups

- Stereo 2:1 Input Multiplexer

- Stereo Full Differential Input

- PC Beep Input

- Low Power Consumption at Shutdown Mode 150mA Typical

- Excellent Click/Pop Noise Suppression

- Thermal Shutdown Protection

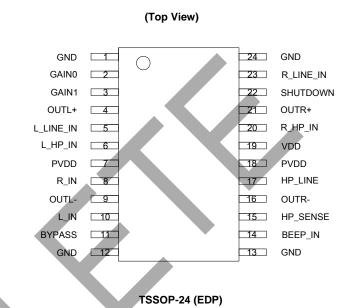

## **Pin Assignments**

Applications

Notebook PC Portable Media Player

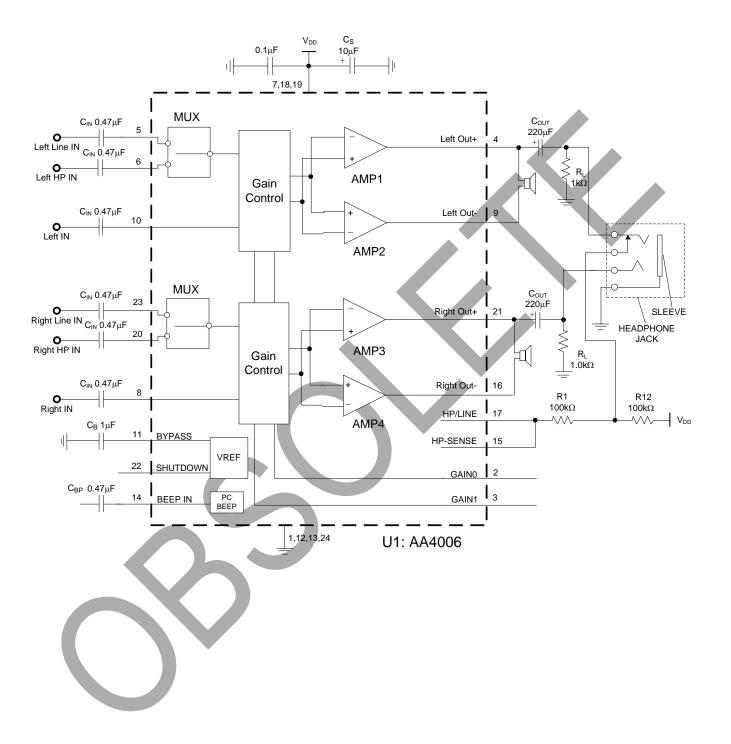

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number    | Pin Name  | Function                                                                                |

|---------------|-----------|-----------------------------------------------------------------------------------------|

| 1, 12, 13, 24 | GND       | Ground reference, it is better to connect with thermal pad                              |

| 2             | GAIN0     | Internal gain setup 0, see table 1 below                                                |

| 3             | GAIN1     | Internal gain setup 1, see table 1 below                                                |

| 4             | OUTL+     | Left channel positive output                                                            |

| 5             | L_LINE_IN | Left channel line input                                                                 |

| 6             | L_HP_IN   | Left channel headphone input                                                            |

| 7, 18         | PVDD      | Power supply for output stage                                                           |

| 8             | R_IN      | Right channel common input for differential input, AC ground for single-<br>ended input |

| 9             | OUTL-     | Left channel negative output                                                            |

| 10            | L_IN      | Left channel common input for differential input, AC ground for single-<br>ended input  |

| 11            | BYPASS    | Internal reference voltage pin, connect a $1.0\mu F$ ceramic capacitor to GND           |

| 14            | BEEP_IN   | Beep signal input pin                                                                   |

| 15            | HP_SENSE  | SE, BTL mode switch pin,<br>L – BTL mode,<br>H – SE mode                                |

| 16            | OUTR-     | Right channel negative output                                                           |

| 17            | HP_LINE   | Headphone, line input select pin,<br>L – line input,<br>H – headphone input             |

| 19            | VDD       | Power supply for other analog circuit                                                   |

| 20            | R_HP_IN   | Right channel headphone input                                                           |

| 21            | OUTR+     | Right channel positive output                                                           |

| 22            | SHUTDOWN  | Shutdown mode select,<br>L – shutdown enable,<br>H – shutdown disable, normal work      |

| 23            | R_LINE_IN | Right channel line input                                                                |

|               |           |                                                                                         |

# Table 1: Gain vs. Gain0, Gain 1 Logic Level

| GAIN0 | GAIN1 | HP_SENSE | Mode | Gain   |

|-------|-------|----------|------|--------|

| L     | L     | L        | BTL  | 6dB    |

| L     | н     | L        | BTL  | 10dB   |

| н     | L     | L        | BTL  | 15.6dB |

| н     | н     | L        | BTL  | 21.6dB |

| Х     | х     | Н        | SE   | 4.1dB  |

## Absolute Maximum Ratings (Note 1)

|                   |                                      |                              | 1    |

|-------------------|--------------------------------------|------------------------------|------|

| Symbol            | Parameter                            | Rating                       | Unit |

| V <sub>DD</sub>   | Power Supply Voltage                 | 6.0                          | V    |

| V <sub>IN</sub>   | Input Voltage                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| PD                | Power Dissipation (Note 2)           | Internally Limited           | -    |

| $\theta_{JA}$     | Thermal Resistance                   | 65                           | °C/W |

| TJ                | Operating Junction Temperature       | +150                         | °C   |

| T <sub>STG</sub>  | Storage Temperature Range            | -65 to +150                  | °C   |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10 sec) | +260                         | °C   |

|                   | ESD (Human Body Model)               | 2000                         | V    |

| ESD               | ESD (Machine Model)                  | 200                          | V    |

Notes: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

2. Chip is soldered to 100mm<sup>2</sup> (4mm x 25mm) copper (top side solder mask) of 1oz. on PCB with 16 x 0.5mm vias.

# **Recommended Operating Conditions**

| Symbol          | Parameter                     | Min | Мах | Unit |

|-----------------|-------------------------------|-----|-----|------|

| V <sub>DD</sub> | Supply Voltage                | 4.5 | 5.5 | V    |

| T <sub>A</sub>  | Operating Ambient Temperature | -40 | +85 | °C   |

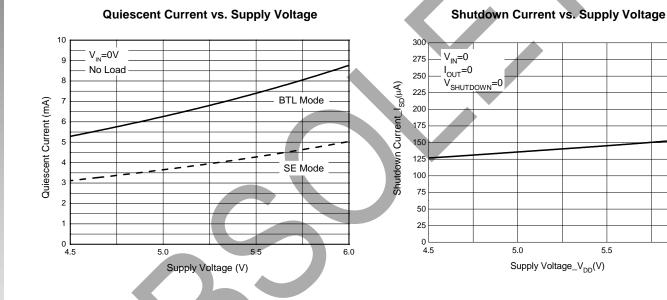

**Electrical Characteristics** ( $V_{DD}$ =5.0V, Gain = 6dB @ BTL mode, 4.1dB @ SE mode,  $T_A$ =+25°C, f=1kHz, 20kHz low pass filter, for SE mode, HP\_SENSE=5.0V, for BTL mode, HP\_SENSE=0V, unless otherwise specified.)

| Symbol            | Pa                | arameter          | Condition                                                                          | Min | Тур  | Мах | Unit              |

|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------|-----|------|-----|-------------------|

|                   |                   |                   | SE mode, V <sub>IN</sub> =0, I <sub>O</sub> =0                                     | -   | 3.5  | 7   | _                 |

| IDD               | Quiescent Current |                   | BTL mode, V <sub>IN</sub> =0, I <sub>O</sub> =0                                    | -   | 6.5  | 12  | mA                |

| I <sub>SD</sub>   | Shutdown Current  |                   | V <sub>SHUTDOWN</sub> =0V                                                          | -   | 150  | 300 | μA                |

|                   |                   | HP_SENSE, HP_LINE | -                                                                                  | 4.0 | -    | -   | V                 |

| VIH               | High Logic Level  | GAIN0, GAIN1      | -                                                                                  | 3.0 | -    |     | V                 |

|                   |                   | SHUTDOWN          | -                                                                                  | 2.0 |      | -   | V                 |

|                   |                   | HP_SENSE, HP_LINE | -                                                                                  | -   | -    | 3.0 | v                 |

| VIL               | Low Logic Level   | GAIN0, GAIN1      | -                                                                                  | -   | -    | 2.0 | V                 |

|                   |                   | SHUTDOWN          | -                                                                                  | -   | -    | 0.8 | V                 |

| -                 | Thermal Shutdown  | n Temperature     | -                                                                                  | -   | +165 | -   | °C                |

| -                 | Hysteresis Tempe  | rature Window     | -                                                                                  | -   | +35  | -   | °C                |

| BEEP              | •                 |                   |                                                                                    |     |      |     |                   |

| V <sub>BP</sub>   | Input Amplitude   |                   | -                                                                                  | 2.5 | -    | -   | V <sub>P</sub> -P |

| G <sub>BP</sub>   | Gain              |                   | $C_{BP}=0.47\mu$ F, f=1kHz, D=50%<br>square wave form,<br>V <sub>BP</sub> =3.3Vp-p |     | 0.3  | -   | V/V               |

| SE Mode           |                   |                   |                                                                                    |     |      |     |                   |

|                   |                   |                   | THD+N=1%, R <sub>L</sub> =32Ω                                                      | -   | 90   | -   |                   |

|                   |                   |                   | THD+N=10%, RL=32Ω                                                                  | -   | 110  | -   | -                 |

| Po                | Output Power      |                   | THD+N=1%, RL=16Ω                                                                   | -   | 180  | -   | mW                |

|                   |                   |                   | THD+N=10%, RL=16Ω                                                                  | -   | 220  | -   |                   |

| THD+N             | Total Harmonic D  | istortion + Noise | P <sub>O</sub> =75mW, R <sub>L</sub> =32Ω                                          | -   | 0.03 | -   | %                 |

| S/N               | Signal to Noise F |                   | P <sub>O</sub> =75mW, R <sub>L</sub> =32Ω                                          | -   | 95   | -   | dB                |

| X <sub>TALK</sub> | Crosstalk         |                   | f=1kHz                                                                             | -   | -90  | -   | dB                |

| PSRR              | Power Supply Re   | jection Ratio     | C <sub>B</sub> =1µF, f=1kHz,<br>V <sub>RIPPLE</sub> =0.2V <sub>RMS</sub>           | -   | 60   | -   | dB                |

| V <sub>NO</sub>   | Output Noise      | •                 | f=20Hz to 20kHz, RL=32 $\Omega$                                                    | -   | 20   | -   | $\mu V_{RMS}$     |

| BTL Mode          |                   |                   |                                                                                    |     |      |     |                   |

|                   | Output Offset Vol | tage              | V <sub>IN</sub> =0V, no load                                                       | -   | ±5   | ±25 | mV                |

|                   |                   |                   | THD+N=1%, $R_L=3\Omega$                                                            | -   | 2.1  | -   |                   |

|                   |                   |                   | THD+N=10%, R <sub>L</sub> =3Ω                                                      | -   | 2.7  | -   |                   |

|                   |                   |                   | THD+N=1%, $R_L=4\Omega$                                                            | -   | 1.8  | -   | 1                 |

| Po                | Output Power      |                   | THD+N=10%, RL=4 $\Omega$                                                           | -   | 2.3  | -   | W                 |

|                   |                   |                   | THD+N=1%, $R_L=8\Omega$                                                            | -   | 1.2  | -   |                   |

|                   |                   |                   | THD+N=10%, RL=8Ω                                                                   | -   | 1.5  | -   |                   |

Electrical Characteristics (V<sub>DD</sub>=5.0V, Gain = 6dB @ BTL mode, 4.1dB @ SE mode, T<sub>A</sub>=+25°C, f=1kHz, 20kHz low pass filter, for SE mode, HP\_SENSE=5.0V, for BTL mode, HP\_SENSE=0V, unless otherwise specified.) (Cont.)

| Symbol            | Parameter                         | Condition                                                          | Min | Тур  | Мах | Unit              |

|-------------------|-----------------------------------|--------------------------------------------------------------------|-----|------|-----|-------------------|

| THD+N             | Total Harmonic Distortion + Noise | $P_0=1W, R_L=4\Omega$                                              | -   | 0.08 | -   | %                 |

| S/R               | Signal to Noise Ratio             | $P_0=1W, R_L=4\Omega$                                              | -   | 100  | -   | dB                |

| X <sub>TALK</sub> | Crosstalk                         | f=1kHz                                                             | -   | -100 | -   | dB                |

| PSRR              | Power Supply Rejection Ratio      | $C_B=1\mu F$ , f=1kHz,<br>V <sub>RIPPLE</sub> =0.2V <sub>RMS</sub> | -   | 70   | -   | dB                |

| V <sub>NO</sub>   | Output Noise                      | f=20Hz to 20kHz, $R_L=8\Omega$                                     | -   | 18   |     | μV <sub>RMS</sub> |

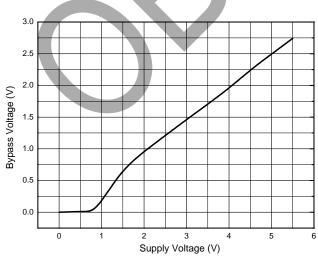

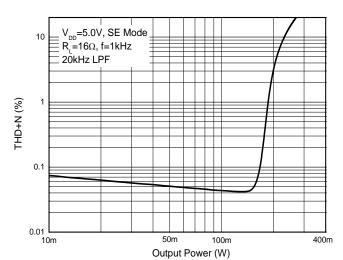

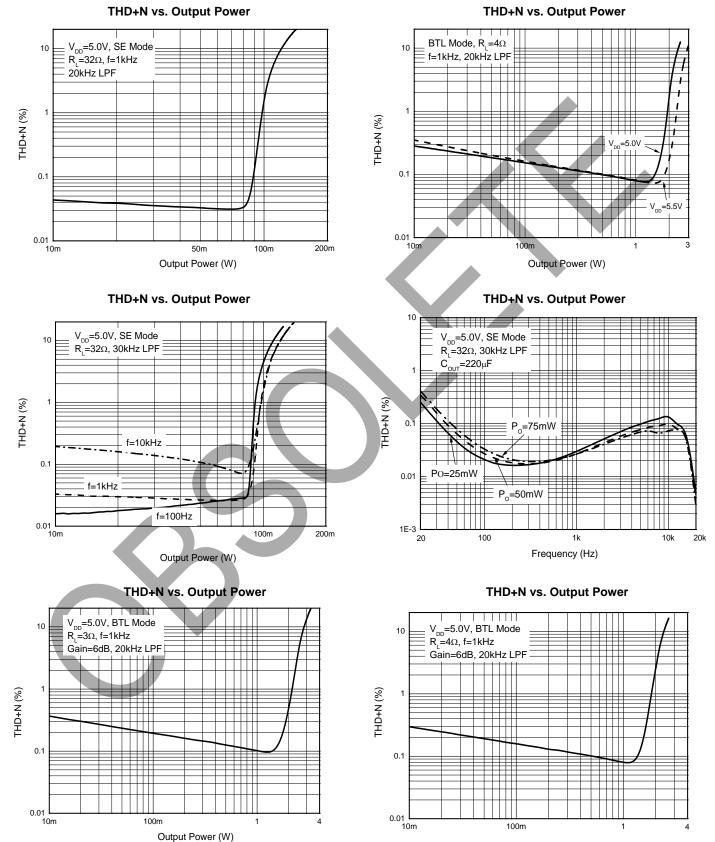

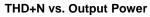

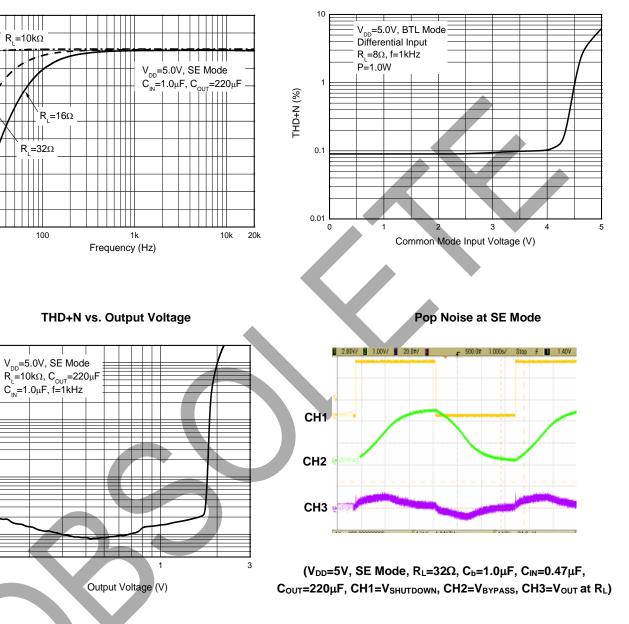

# **Performance Characteristics**

Bypass Voltage vs. Supply Voltage

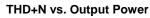

### THD+N vs. Output Power

5.5

6.0

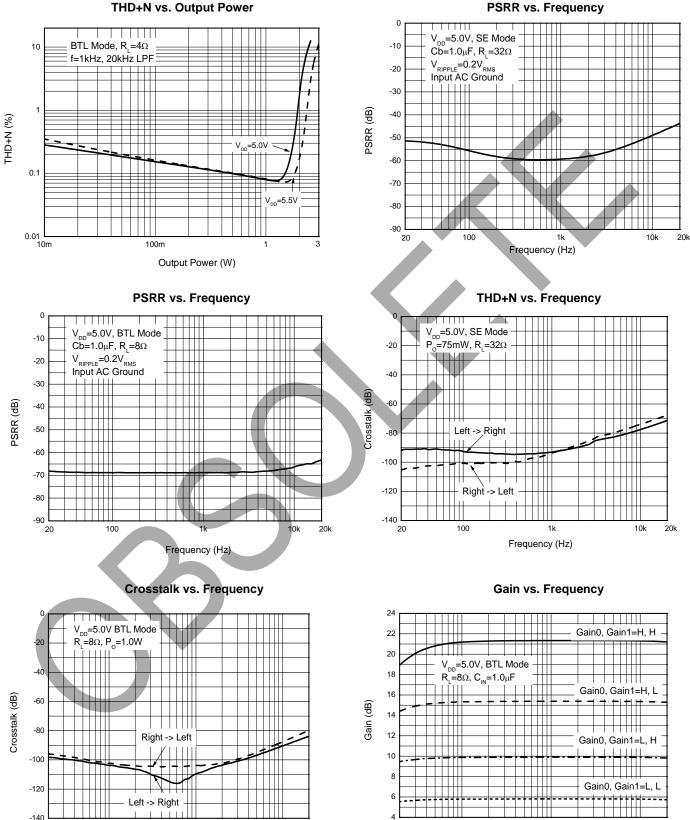

## Performance Characteristics (Cont.)

## Performance Characteristics (Cont.)

© Diodes Incorporated

Frequency (Hz)

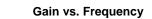

# Performance Characteristics (Cont.)

100

Frequency (Hz)

-140

20

20

100

1k

Frequency (Hz)

10k

20k

10k

20k

6

4

2

0

-2

-4

-6

10

1

0.1

0.01

100m

THD+N (%)

20

AA4006

### Performance Characteristics (Cont.)

$R_1 = 10 k\Omega$

R,=32Ω

100

## **Application Information**

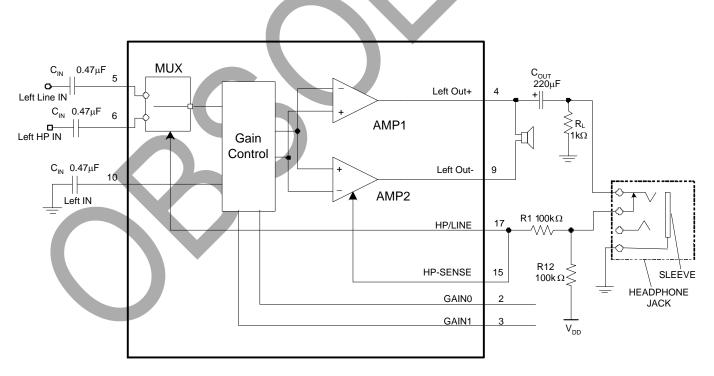

#### SE/BTL Mode, HP\_SENSE Pin

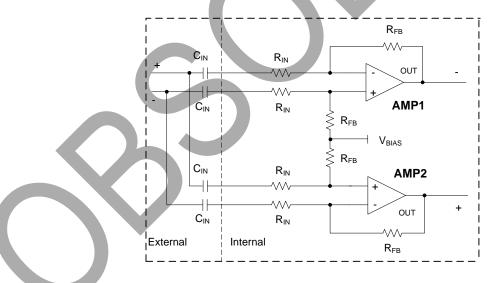

The AA4006 can operate under 2 types of output configuration, SE (Single-Ended) mode and BTL (Bridged Tied Load) mode, determined by HP\_SENSE pin's logic level. (Here is the discussion about left channel only, it can equally apply to right channel.)

When HP\_SENSE pin is held low which sets the chip in BTL mode, both AMP1 and AMP2 are turned on. AMP2 has the same gain with AMP1 except 180 degree phase shift. Because the DC component (output bias voltage from AMP1 and AMP2, approx. 1/2 V<sub>DD</sub>) between OUT+ and OUT- is canceled, there is no necessity to use DC block capacitors for speaker load. In BTL mode, output voltage swing across load is about 2 times that in SE mode, so there is about 4 times output power compared to SE mode with same load and input. (See Figure 1)

If applying high level to HP\_SENSE pin which sets the chip in SE mode, AMP2 unit is turned off with high impedance. There is no current loop between OUT+ and OUT-, the speaker is naturally disabled without any hardware change. The output audio signal rides on bias voltage at OUT+ (output bias voltage from AMP1 and AMP2, approx.  $1/2 V_{DD}$ ), so it has to use a capacitor C<sub>OUT</sub> to block DC bias voltage and couple AC signal to headphone load.

It is recommended to connect HP\_SENSE to the headphone jack switch pin illustrated in Figure 1. When headphone plug is not inserted, the voltage of HP\_SENSE pin is determined by voltage divider formed by R<sub>L</sub> and R<sub>12</sub>. For given resistors' value in Figure 1, R<sub>L</sub>=1k $\Omega$ , R<sub>12</sub>=100k $\Omega$  (Assuming V<sub>DD</sub>=5.0V), DC voltage at HP\_SENSE node is about 49.5mV. AC signal equals output amplitude of OUT+ through C<sub>OUT</sub>, the maximum peak-peak voltage is no greater than V<sub>DD</sub>, so the positive maximum voltage of HP\_SENSE node will be no greater than 2.5V+49.5mV=2.55V(DC voltage plus AC voltage), which is less than HP\_SENSE input high level minimum value (4.0V). That means the chip works in BTL mode reliably and there is no risk of operation mode switch between SE and BTL. When headphone plug is inserted, as the R<sub>L</sub> is disconnected from R<sub>12</sub>, the voltage of HP\_SENSE pin is pulled up by R<sub>12</sub> to V<sub>DD</sub> sets the chip in SE mode.

HP\_SENSE pin can also be connected to MCU I/O port directly to switch the operation mode between SE and BTL.

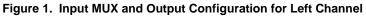

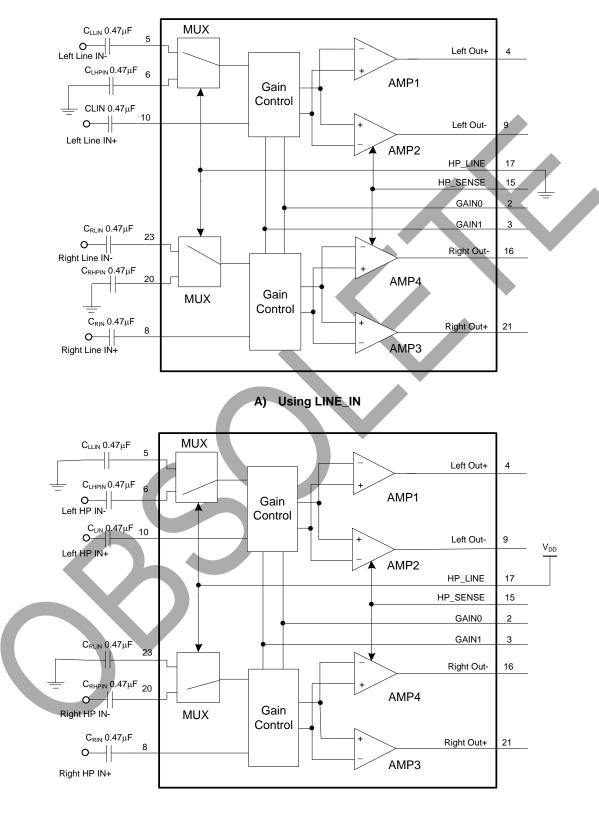

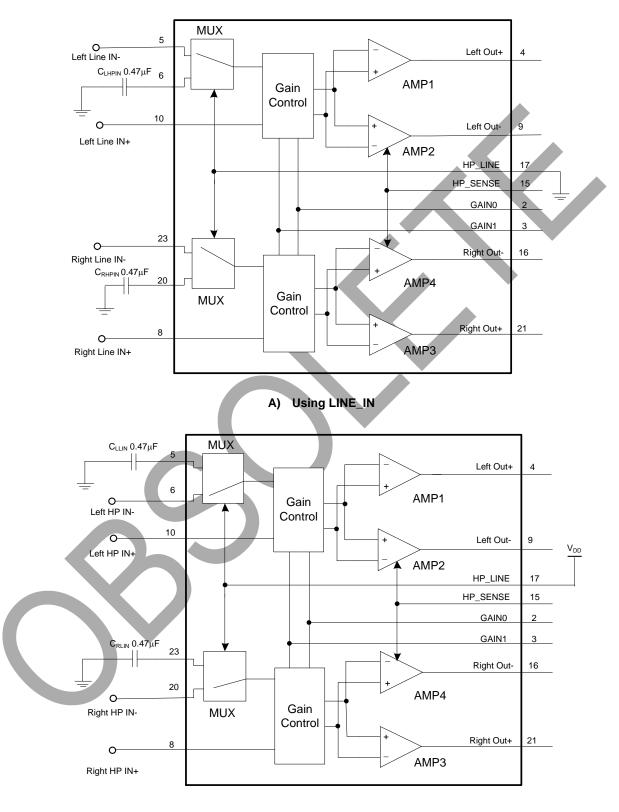

### Input MUX, Single-Ended Input and Differential Input

The AA4006 offers the capability to use 2 individual stereo inputs: headphone input and line input. For a single-ended input, the common input terminal pins (L\_IN, R\_IN) should be connected to ground through a capacitor, also the size of  $C_{LIN}$  ( $C_{RIN}$ ) has to be the same as  $C_{LLIN}$  ( $C_{RLIN}$ ),  $C_{LHPIN}$  ( $C_{RHPIN}$ ). Line input and headphone input are selected by switching HP\_LINE pin. When HP\_LINE is pulled high, the headphone input (L\_HP\_IN, R\_HP\_IN) is selected. When HP\_LINE is held low, the line input (L\_LINE\_IN, R\_LINE\_IN) is selected. If the input signals are differential, only one stereo signal is permitted because share common input terminal pin (L\_IN, R\_IN), both headphone input and line input can be formed into differential pair with common input terminal. (See Figure 3)

With differential input configuration, the input coupling capacitors of differential pair can be removed if DC bias voltage of input source is within input common- mode voltage range, refer to Figure THD+N vs. Common Mode Input Voltage in Performance Characteristics.

B) Using HP\_IN

#### Figure 3. Differential Input with Input Coupling Capacitors

B) Using HP\_IN

Figure 4. Differential Input without Input Coupling Capacitors

### $C_{\text{IN}},\,C_{\text{OUT}},\,C_{\text{B}}$ and $C_{\text{S}}$ (Power Supply) Selection

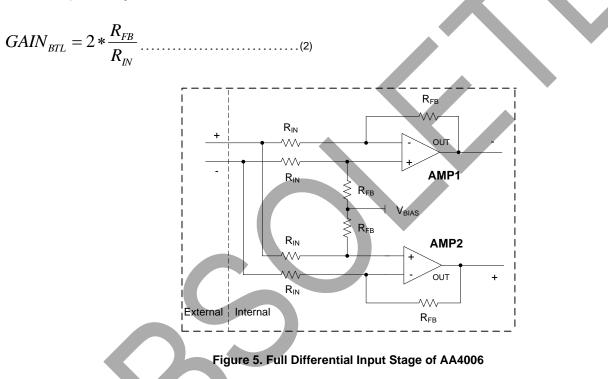

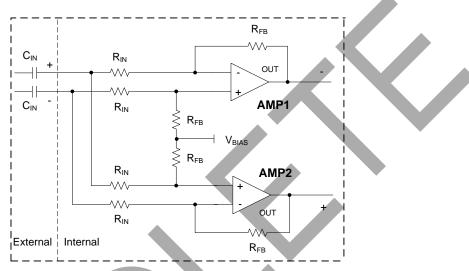

Although there is no necessary to use input coupling capacitors in differential input if DC voltage of input is within common-mode input voltage range. The AA4006 allows using input capacitors  $C_{IN}$  to accommodate different DC level between input source(like Audio D-A converter) and bias voltage (about 1/2  $V_{DD}$ ), especially in single-ended input mode which is popularly used in most applications. Input stage of AA4006 is illustrated as Figure 5, it is a full differential architecture, which consists of input resistor,  $R_{IN}$  and feedback resistor,  $R_{FB}$ .

In SE mode, pass-band gain is,

In BTL mode, pass-band gain is,

The typical input resistance, feedback resistance of AA4006 at each gain setting are showed in the table below.

| GAIN0 | GAIN1 | HP_SENSE | GAIN (dB) | R <sub>IN</sub> (Ω) | R <sub>FB</sub> (Ω) |

|-------|-------|----------|-----------|---------------------|---------------------|

| 0     | 0     | 0        | 6         | 90                  | 90                  |

| 0     | 1     | 0        | 10        | 70                  | 110                 |

| 1     | 0     | 0        | 15.6      | 45                  | 135                 |

| 1     | 1     | 0        | 21.6      | 25                  | 154                 |

| х     | х     | 1        | 4.1       | 70                  | 110                 |

Input capacitors C<sub>IN</sub> and input resistors R<sub>IN</sub> form a first order High Pass Filter, which determines the lower corner frequency according to the equation below.

It is a little different from the classic equation according to Figure 6.

#### A) AA4006 Input Configuration with Input Capacitor

B) Classic Input Configuration with Input Capacitor

#### Figure 6. Input Configuration with Input Capacitor, CIN

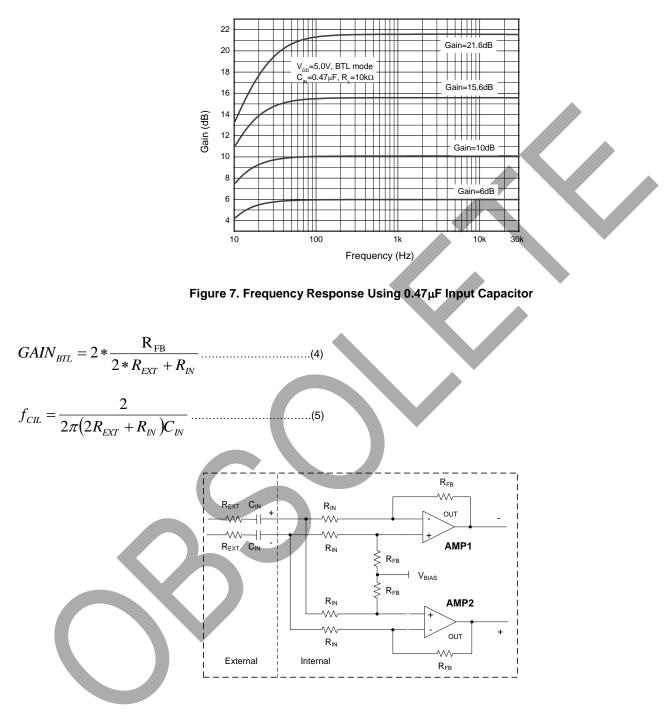

Input resistance varies with gain setting, also the absolute resistance of  $R_{IN}$  may drift ±20% due to fab process. To ensure the minimum cut-off frequency within the audible range, the input capacitor ( $C_{IN}$ ) has to be greater than 0.33µF. The low ESR ceramic capacitor of 0.47µF is recommended. See Figure 7 for frequency response using 0.47µF  $C_{IN}$ . However, using bigger size of  $C_{IN}$  will affect pop noise of AA4006.

If using an external resistor R<sub>EXT</sub> in series with input capacitor C<sub>IN</sub>, the closed-loop gain and cut-off frequency can be calculated by equations below.

# Application Information (Cont.)

Figure 8. Using an External Resistor,  $R_{\text{EXT}}$  in Series with Input Capacitor,  $C_{\text{IN}}$

Similarly, for output stage in SE mode, output capacitor (C<sub>OUT</sub>) and headphone load (R<sub>HP</sub>) also form a first order High Pass Filter, and its lower cut-off frequency is determined by equation 6.

$$f_{COL} = \frac{1}{2\pi R_{HP} * C_{OUT}}$$

.....(6)

| C <sub>OUT</sub> (µF) | Headphone Load (Ω) | Lower Cut-off Frequency (Hz) |

|-----------------------|--------------------|------------------------------|

| 220                   | 16                 | 45.2                         |

| 220                   | 32                 | 22.6                         |

| 330                   | 16                 | 30                           |

| 330                   | 32                 | 15                           |

The purpose of the bypass capacitor ( $C_B$ ) is to filter noise, reduce total harmonic distortion plus noise, and improve power supply rejection ratio performance. Tantalum or ceramic capacitor of  $1.0\mu$ F with low ESR is recommended, and it should be placed as close as possible to the chip in PCB layout. This capacitor affects the pop noise performance furthest by changing the ramp of charge and/or discharge.

The below table shows output noise in each gain under the condition of 1.0µF bypass capacitor. Unit: µVrms.

| -        |                                              |                     | Filter: 22Hz ~ 22kHz | A-Weighted Filter |

|----------|----------------------------------------------|---------------------|----------------------|-------------------|

|          | C <sub>OUT</sub> =220μF, R <sub>L</sub> =16Ω |                     | 22                   | 16                |

| SE Mode  | $C_{OUT}=220\mu F, R_L=32\Omega$             |                     | 23                   | 17                |

|          |                                              | Gain0, Gain1 = 0, 0 | 18.5                 | 13.5              |

|          |                                              | Gain0, Gain1 = 0, 1 | 23                   | 17                |

|          | $R_L=4\Omega$                                | Gain0, Gain1 = 1, 0 | 32                   | 24.5              |

|          |                                              | Gain0, Gain1 = 1, 1 | 46.5                 | 37                |

| BTL Mode |                                              | Gain0, Gain1 = 0, 0 | 19                   | 14                |

|          |                                              | Gain0, Gain1 = 0, 1 | 24                   | 18                |

|          | R <sub>L</sub> =8Ω                           | Gain0, Gain1 = 1, 0 | 33.5                 | 25.5              |

|          |                                              | Gain0, Gain1 = 1, 1 | 52                   | 39                |

For AA4006 power supply, it is better to use an individual power source generated from voltage regulator split from video, digital circuit units in system. For power supply bypass capacitor (C<sub>S</sub>), it is recommended to use one low ESR electrolytic or tantalum capacitor from  $4.7\mu$ F to  $10\mu$ F in parallel with  $0.1\mu$ F ceramic capacitor which is located close to the chip.

## Shutdown

AA4006 has a shutdown feature to reduce power consumption during non-use operation. If apply low level to shutdown pin, output amplifiers, bias circuit will be turned off, the current drawn from V<sub>DD</sub> is about 100µA. However, the Beep Detect circuitry is always ready to give alert on speaker load once apply any valid signal into BEEP\_IN pin. The SHUTDOWN pin should be pulled high during normal operation, and it should never be left floating to prevent the unpredictable status of the chip.

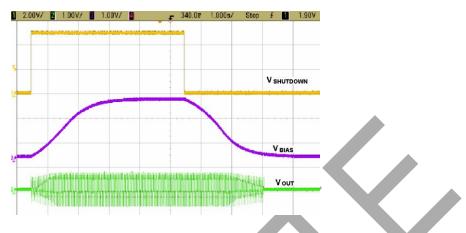

However, the music signal will be output instantly once the SHUTDOWN pin is applied to logic level from low to high. When the SHUTDOWN pin changes from high to low, output will be present until bias voltage drops to approx 0.1V. See Figure 9 for time relationship between shutdown, bias voltage and output.

Figure 9. Time Chart for V<sub>SHUTDOWN</sub>, V<sub>BIAS</sub> and V<sub>OUT</sub>

#### Optimizing Click/Pop Noise

The AA4006 includes optimized circuits to suppress Click/Pop noise during power up/power down transition.

In BTL mode, AA4006 can reduce most common mode signal also including Click/Pop noise due to symmetrical output.

In SE mode, optimized ramp for rise/fall edge of bias can significantly reduce Click/Pop noise generated by output capacitor ( $C_{OUT}$ ) charge and/or discharge. Smoothing rise/fall edge of DC bias voltage is a quite important method. Another way is to prolong charge/discharge time which can shape power spectrum of output, and this makes some frequencies outside of the human audible range (20Hz to 20kHz). So external components (including  $C_B$ ,  $C_{IN}$ ,  $C_{OUT}$  and headphone load) will affect pop noise performance. The recommended components are,  $C_B=1.0\mu$ F,  $C_{IN}=0.47\mu$ F,  $C_{OUT}=220\mu$ F,  $32\Omega$  for headphone load. Under given conditions, the maximum peak-peak voltage of pop noise is less than 15mV (See Figure Pop Noise at SE Mode). If using 16 $\Omega$  headphone, the voltage of pop noise will decrease accordingly.

#### **Beep Input**

Beep input feature is used in computer system for alerting. A beep signal can be sent directly from a computer. If peak-peak voltage of beep signal applied to BEEP\_IN pin (pin14) exceeds a certain voltage (typical 1/2 V<sub>DD</sub>), the feature will be activated automatically, then AA4006 will be forced in BTL mode with the fixed gain of 0.3V/V, both LINE\_IN and HP\_IN are deselected, the logic level of HP\_SENSE, HP\_LINE, GAIN0, GAIN1 and SHUTDOWN is ignored. Once beep signal is removed from the chip, the AA4006 will return to the previous operation mode, gain settings.

The preferred beep signal is a square wave or pulse train, the preferred input is DC-coupled. If using AC-coupled, assuming beep input capacitor is  $0.47\mu$ F, the input voltage is  $3.3 V_{P-P}$  square wave, the beep signal should have a minimum of 10 cycles.

#### Power Dissipation, Efficiency and Thermal Design Consideration

For Class AB amplifiers, equation 7 is the basic equation of efficiency worked in BTL mode,

Here  $\mathsf{V}_\mathsf{P}$  is output peak voltage across the load.

Thermal dissipation becomes major concern when delivering more power into speaker especially in BTL mode. The maximum allowed power dissipation can be calculated by equation below which is determined by thermal resistance of AA4006 package.

Here  $T_{JMAX}$  is maximum operating junction temperature of +150°C,  $T_A$  is ambient temperature,  $\theta_{JA}$  is thermal resistance from junction to ambient. For TSSOP-24(EDP) package, it is 65°C/W given in datasheet.

Assuming T<sub>A</sub> is +25°C, the maximum allowed power dissipation is about 1.92W according to equation 8.

There is another equation about power dissipation which is determined by power supply voltage and load resistance under a certain application.

The above equation expresses total power dissipation, dominated by dual channels, quiescent current. It is a quadratic equation with the negative coefficient of output voltage variation (V<sub>P</sub>), there is always a maximum showed as below.

If power dissipation calculated by application is larger than the package permitted, it is necessary to use larger copper plane under the chip, or assemble an additional heat sink, or use forced-air cooling to keep ambient temperature around the chip low, or increase load resistance, or decrease power supply voltage.

For example, assuming  $V_{DD}$ =5.0V, speaker load  $R_{SP}$ =4.0 $\Omega$ , stereo in BTL mode, the maximum power dissipation, includes 2 channels, plus quiescent power dissipation, dominated by quiescent current.

$$P_{DBTLMAX} = \frac{4V_{DD}^{2}}{\pi^{2}R_{L}} + V_{DD}*I_{DD}$$

$$= \frac{4*5^{2}}{\pi^{2}*4} + 5.0*0.0065$$

$$= 2.56W$$

That is to say, to make sure AA4006 can output power into stereo  $4\Omega$  speakers continuously, the maximum ambient temperature should be no more than,

$$T_{A} = T_{JMAX} - \theta_{JA} * P_{DT}$$

= 150 - 65 \* 2.56

= 16.4°C

The maximum power dissipation is achieved only when output power per-channel equals  $2*V_{DD}^{2/\pi}*R_{SP}$ . If actual output power is not this data, power dissipation will be less than 2.56W.

When junction temperature exceeds about +165°C, OTSD feature will be enabled, that turns off output amplifiers to prevent damaging the chip. Once junction temperature drops lower than +130°C, the chip will work again automatically.

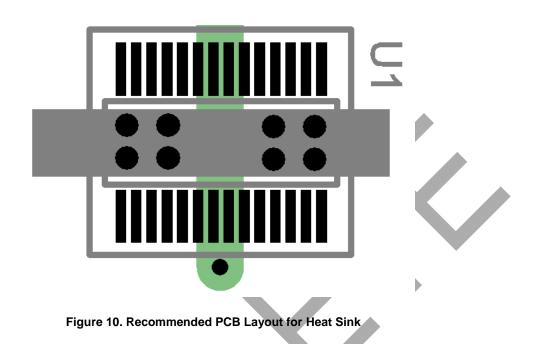

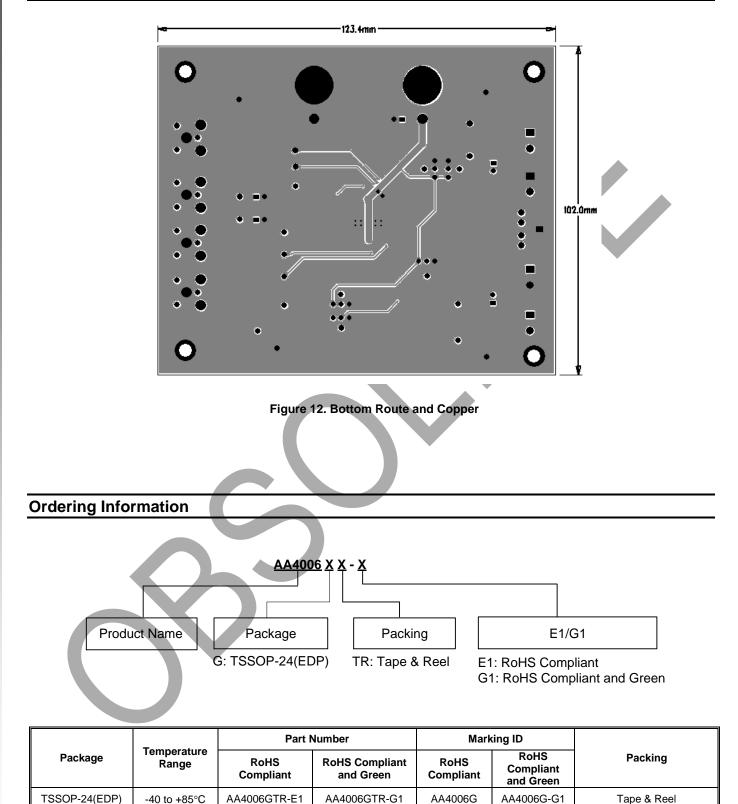

There is an exposed thermal pad on the bottom of the chip to provide the direct thermal path from die to heat sink. It is recommended to use copper on the surface of Printed Circuit Board (PCB) as heat sink. To dig some matrix regular holes under chip, remove mask of this area copper, and make sure to keep them contact well when soldering on PCB are also recommended. (See Figure 10)

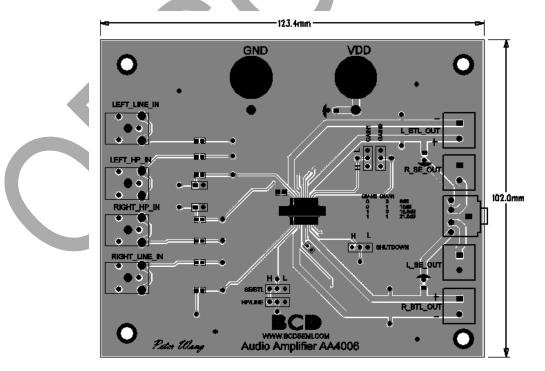

#### **Recommended PCB Layout**

Using wide traces for power supply, BTL outputs to reduce power losses caused by parasitic resistance is recommended. It is also recommended to place bypass capacitor, and power supply decouple capacitor as close as possible to the chip.

Figure 11. Top Route and Copper

# Application Information (Cont.)

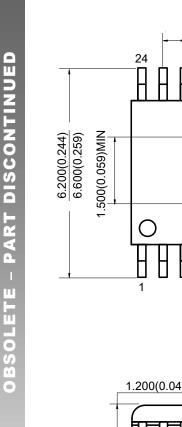

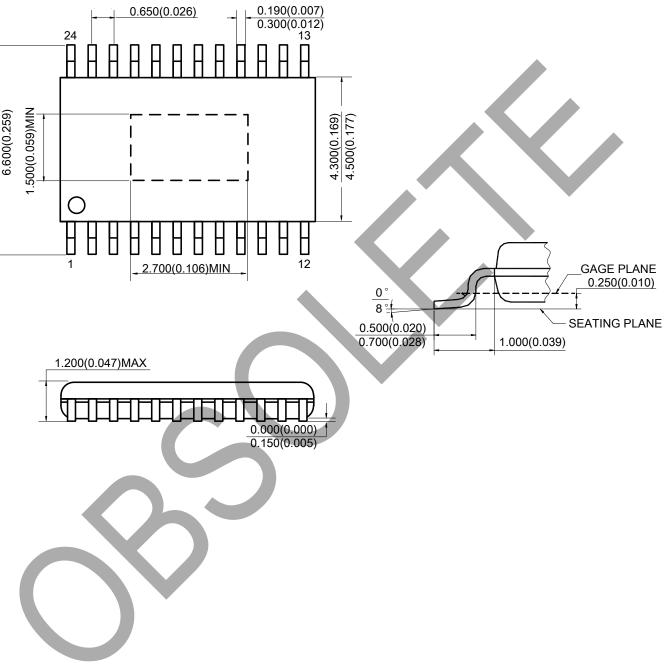

# Package Outline Dimensions (All dimensions in mm(inch).)

(1) Package Type: TSSOP-24 (EDP)

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2018, Diodes Incorporated

www.diodes.com