AP43771V

#### HIGH-PERFORMANCE USB PD CONTROLLER

### Description

The AP43771V is a highly integrated USB Type- $C^{\otimes}$  power delivery controller targeted for USB Type-C adapter and charger application. It is compatible with Qualcomm<sup>®</sup> QC4/4+/QC5 protocol, which supports USB power delivery specification Rev3.1 V1.2 (including optional PPS support).

The AP43771V can support PPS APDO (Augmented Power Data Object) with 20mV/step voltage resolution and 50mA/step current resolution for power management. Also embedded is cable-loss compensation and SOP command for e-Marker detection.

The AP43771V can provide a robust protection scheme with built-in OVP/OCP/SCP/OTP features.

Dedicated part number AP43771VFBZ-13-FR01 (W-DFN3030-14 (Type A1)) with standard firmware provides a preloaded 8-powerprofile menu. System manufacturers could easily select a desired power profile (Constant Voltage CV and Constant Current CC) through a single resistor attached to the relevant pin (OTP pin) to meet output power requirements of a USB PD charger or adaptor.

Supporting emerging multiple Type-C PD applications, the AP43771V (W-QFN4040-24 (Type A1)) with customized firmware can be used for implementing smart power sharing scheme. It monitors status of other I2C interface connected ports and leverages the embedded MCU for command execution through I2C interface to re-allocate desired power profile for each Type-C port.

### Features

- Compatible with USB PD Rev3.1 V1.2

- USB-IF PD Certificated with TID: 4305

- Qualcomm QC4/4+/QC5 Protocol Certificated (QC20201127203)

- 16kB OTP (One-Time Programmable) Memory

- Built-in Regulator for CV and CC Control

- Support SCP/OTP/OVP/UVP with Auto Restart

- Support Power Saving Mode

- Driver for Output Enable nMOS Switch

- Current Sensing with 10mΩ Resistance for Better Efficiency

- Support E-Marker Cable Detection

- Support I2C Interface (W-QFN4040-24 (Type A1) Only)

- Operating Voltage Range: 3.3V to 24V

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative. <u>https://www.diodes.com/guality/product-definitions/</u>

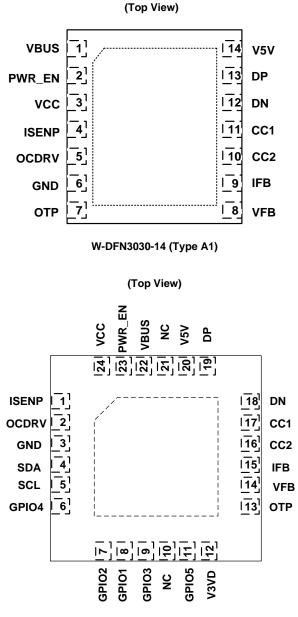

### **Pin Assignments**

W-QFN4040-24 (Type A1)

### Applications

- Type-C USB adapters/chargers

- USB PD converters

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

Notes:

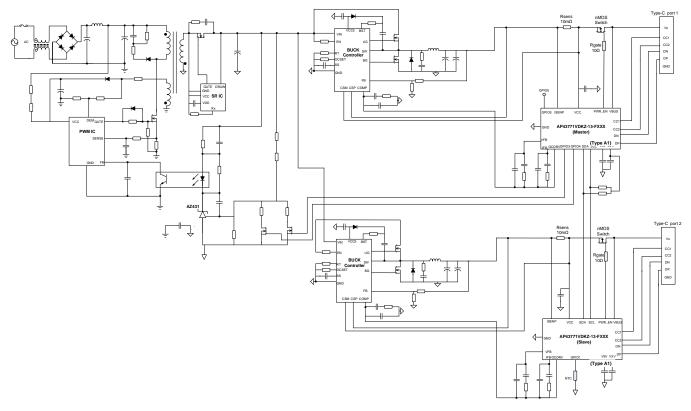

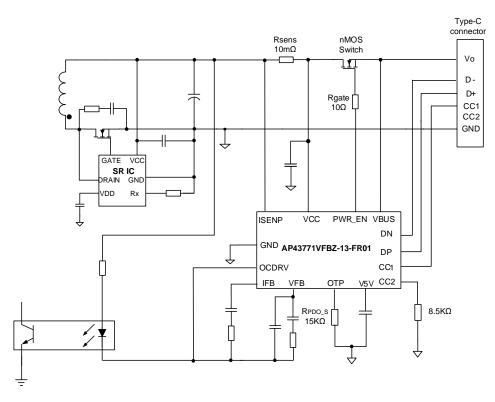

# **Typical Applications Circuit**

Figure 1. Traditional 65W Single Type-C Port USB PD Charger Application with AP43771VFBZ-13-FR01 (Standard Firmware Inside)

Figure 2. Dual C-Ports USB PD Charger Application with AP43771VDKZ-13-FXXX (Customized Firmware Inside)

# **Pin Descriptions**

| W-DFN3030- | 14 (Type A1) | Function                                                                                                                                                                                                                                                                    |

|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Name     |                                                                                                                                                                                                                                                                             |

| 1          | VBUS         | Output Terminal for Discharge Path.                                                                                                                                                                                                                                         |

| 2          | PWR_EN       | nMOS Switch gate control to switch the nMOS on or off.                                                                                                                                                                                                                      |

| 3          | VCC          | The Power Supply of the IC. A 1µF cap is required to connect this pin to GND pin.                                                                                                                                                                                           |

| 4          | ISENP        | Current Sense Positive Node, connect to the positive node of the external current sensing resistor.                                                                                                                                                                         |

| 5          | OCDRV        | CC/CV Output. Open-Drain Output for Optocoupler.                                                                                                                                                                                                                            |

| 6          | GND          | Ground                                                                                                                                                                                                                                                                      |

| 7          | OTP          | Functional option 1: 100µA Current Source output for NTC connected to ground. This NTC is used to monitor temperature variation.<br>Functional option 2: for dedicated part number AP43771VFBZ-13-FR01, connect a resistor to ground for selecting a desired power profile. |

| 8          | VFB          | CV Input. Negative Node of CV OPAMP for Optocoupler.                                                                                                                                                                                                                        |

| 9          | IFB          | CC Input. Negative Node of CC OPAMP for Optocoupler.                                                                                                                                                                                                                        |

| 10         | CC2          | Type-C Configuration Channel 2 (CC2). The CC2 pin detects, configures, and manages the connections across a USB Type-C cable.                                                                                                                                               |

| 11         | CC1          | Type-C Configuration Channel 1 (CC1). The CC1 pin detects, configures, and manages the<br>connections across a USB Type-C cable.                                                                                                                                            |

| 12         | DN           | Type-C_DN                                                                                                                                                                                                                                                                   |

| 13         | DP           | Type-C_DP                                                                                                                                                                                                                                                                   |

| 14         | V5V          | Output of the internal 5V LDO with VCC as input. A 1µF cap is required to connect this pin to GND.                                                                                                                                                                          |

| W-QFN4040- | 24 (Type A1) | Eurotian                                                                                                                      |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Name     |                                                                                                                               |

| 1          | ISENP        | Current Sense Positive Node, connect to the positive node of the external current sensing resistor.                           |

| 2          | OCDRV        | CC/CV Output. Open-Drain Output for Optocoupler.                                                                              |

| 3          | GND          | Ground                                                                                                                        |

| 4          | SDA          | I2C Data, need to be pulled up externally.                                                                                    |

| 5          | SCL          | I2C Clock, need to be pulled up externally.                                                                                   |

| 6          | GPIO4        | General-Purpose Input or Output                                                                                               |

| 7          | GPIO2        | General-Purpose Input or Output                                                                                               |

| 8          | GPIO1        | General-Purpose Input or Output                                                                                               |

| 9          | GPIO3        | General-Purpose Input or Output                                                                                               |

| 10         | NC           | No Connection                                                                                                                 |

| 11         | GPIO5        | General-Purpose Input or Output                                                                                               |

| 12         | V3VD         | Output of the internal 3V LDO, connect to a ceramic capacitor.                                                                |

| 13         | OTP          | 100µA Current Source output for NTC connected to ground. This NTC is used to monitor temperature variation.                   |

| 14         | VFB          | CV Input. Negative Node of CV OPAMP for Optocoupler.                                                                          |

| 15         | IFB          | CC Input. Negative Node of CC OPAMP for Optocoupler.                                                                          |

| 16         | CC2          | Type-C Configuration Channel 2 (CC2). The CC2 pin detects, configures, and manages the connections across a USB Type-C cable. |

| 17         | CC1          | Type-C Configuration Channel 1 (CC1). The CC1 pin detects, configures, and manages the connections across a USB Type-C cable. |

| 18         | DN           | Type-C_DN                                                                                                                     |

| 19         | DP           | Type-C_DP                                                                                                                     |

| 20         | V5V          | Output of the internal 5V LDO with VCC as input. A 1µF cap is required to connect this pin to GND.                            |

| 21         | NC           | No Connection                                                                                                                 |

| 22         | VBUS         | Output Terminal for Discharge Path.                                                                                           |

| 23         | PWR_EN       | nMOS Switch gate control to switch the nMOS on or off.                                                                        |

| 24         | VCC          | The power supply of the IC. A 1µF cap is required to connect this pin to GND pin.                                             |

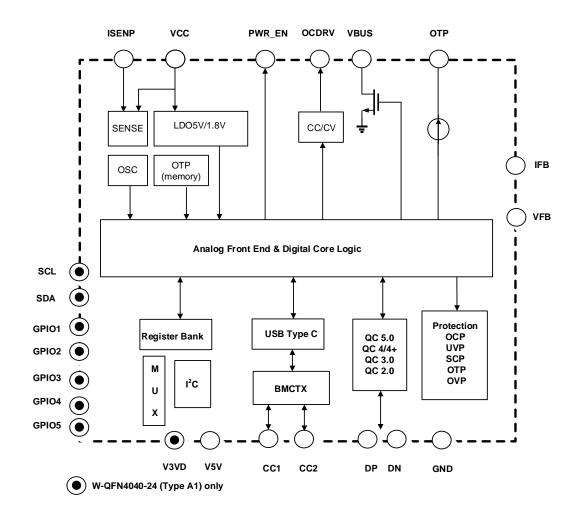

# **Functional Block Diagram**

### Absolute Maximum Ratings (Note 4)

| Symbol                        | Parameter                                                                                                  | Rating                           |    | Unit  |

|-------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------|----|-------|

| Vcc                           | Input Voltage at VCC Pin                                                                                   | -0.3 to 24                       |    | V     |

| Vfb, Vifb, Votp               | Input Voltage at VFB, IFB, OTP Pins                                                                        | -0.3 to 7                        |    | V     |

| Vbus, Vpwr_en, Visenp, Vocdrv | Input Voltage at VBUS, PWR_EN, ISENP, OCDRV Pins                                                           | -0.3 to 24                       |    | V     |

| —                             | Voltage from PWR_EN to VCC Pin                                                                             | -16 to 7                         |    | V     |

| Vv5v                          | Input Voltage at V5V Pin                                                                                   | -0.3 to 7                        |    | V     |

| VCC1, VCC2                    | Input Voltage at CC1, CC2 Pins                                                                             | -0.3 to 7                        |    | V     |

| Vdp, Vdn                      | Input Voltage at DP, DN Pins                                                                               | -0.3 to 7                        |    | V     |

| Vgpi01 - Vgpi05, VSDA, Vscl   | Input Voltage at GPIO1-5, SDA, SCL Pins<br>(Note 5)                                                        | -0.3 to 5                        |    | V     |

| TJ                            | Operating Junction Temperature                                                                             | -40 to +150                      |    | °C    |

| Tstg                          | Storage Temperature                                                                                        | -65 to +150                      |    | °C    |

| TLEAD                         | Lead Temperature (Soldering, 10s)                                                                          | +300                             |    | °C    |

| 0                             | Thermal Resistance (Junction to Ambient)                                                                   | W-DFN3030-14 (Type A1)           | 54 | 80 MM |

| θ」Α                           | (Note 6)                                                                                                   | W-QFN4040-24 (Type A1)           | 28 | °C/W  |

| 0                             | Thermal Resistance (Junction to Case)                                                                      | W-DFN3030-14 (Type A1)           | 34 | 00444 |

| θις                           | (Note 6)                                                                                                   | W-QFN4040-24 (Type A1)           | 16 | °C/W  |

|                               | ESD (Human Body Model) Voltage on DP,<br>DN Pins                                                           | on DP, 6                         |    | kV    |

| _                             | ESD (Human Body Model) Voltage on<br>VBUS, ISENP, PWR_EN, VCC, OCDRV,<br>OTP, V5V, IFB, VFB, CC1, CC2 Pins | JŠ, ISENP, PŴR_EN, VCC, OCDRV, 2 |    | kV    |

| _                             | ESD (Charged Device Model)                                                                                 | 750                              |    | V     |

Notes: 4. Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and Stresses greater than those inside under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability.

When GPIO1-5, SDA, SCL pins are pulled high to a voltage source, it is strongly recommended to series a resistor with minimum 10k value.

Test condition: device mounted on FR-4 substrate PC board, 2oz copper, with the minimum footprint.

# **Recommended Operating Conditions**

| Symbol | Parameter                   | Min | Мах | Unit |

|--------|-----------------------------|-----|-----|------|

| Vcc    | Power Supply Voltage        | 3.3 | 24  | V    |

| Тор    | Operating Temperature Range | -40 | +85 | °C   |

### Electrical Characteristics (@TA = +25°C, unless otherwise specified.)

| Symbol                | Parameter                                                                                            | Condition                         | Min   | Тур  | Max   | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------|-----------------------------------|-------|------|-------|------|

| VCC PIN SECTION       |                                                                                                      |                                   |       |      |       |      |

| V <sub>ST</sub>       | Startup Voltage                                                                                      | _                                 | 2.5   | 2.8  | 3.2   | V    |

| Vuvlo                 | Minimum Operating Voltage                                                                            | _                                 | 2.4   | 2.7  | 3     | V    |

| Vcc_Hys               | Vcc Hysteresis (Vst-VuvLo)                                                                           | _                                 | 0.05  | _    | —     | V    |

| ICC_DEEP SLEEP        | VIN Current in Deep Sleep Mode                                                                       | CC1/2 Detach after 3s<br>Vcc = 5V |       | 550  | 900   | μA   |

| I <sub>CC_OPR</sub>   | Operating Supply Current                                                                             | $V_{CC} = 5V$                     | _     | 3.3  | 6     | mA   |

| VOLTAGE CONTROL       | LOOP SECTION                                                                                         |                                   |       |      |       |      |

| Vref_CV5              | Reference Voltage for 5V CV Control                                                                  | —                                 | 4.85  | 5    | 5.15  | V    |

| Vref_cv9              | Reference Voltage for 9V CV Control                                                                  | _                                 | 8.73  | 9    | 9.27  | V    |

| VREF_CV12             | Reference Voltage for 12V CV Control                                                                 | _                                 | 11.64 | 12   | 12.36 | V    |

| VCABLE                | Cable Compensation (Note 7)                                                                          | _                                 | 22    | 32   | 42    | mV/A |

| los                   | Maximum OCDRV Pin Sink Current                                                                       | Vout = 5V                         | 10    | 16   | 30    | mA   |

| PROTECTION FUNCT      | ION SECTION                                                                                          |                                   |       |      |       |      |

| Vovp5v                | OVP_5V Enable Voltage (Note 8)                                                                       | _                                 | 5.6   | 6    | 6.8   | V    |

| V <sub>OVP9V</sub>    | OVP_9V Enable Voltage (Note 8)                                                                       | _                                 | 9.9   | 10.8 | 12.1  | V    |

| VOVP12V               | OVP_12V Enable Voltage (Note 8)                                                                      | _                                 | 13.2  | 14.4 | 16.2  | V    |

| tdebounce_ovp         | OVP Debounce Time (Note 9)                                                                           | _                                 |       | 90   |       | ms   |

| V <sub>UVP5V</sub>    | UVP_5V Enable Voltage                                                                                | _                                 | 3.3   | 3.7  | 4.4   | V    |

| VUVP9V                | UVP_9V Enable Voltage                                                                                | _                                 | 5.9   | 6.8  | 7.7   | V    |

| VUVP12V               | UVP_12V Enable Voltage                                                                               | _                                 | 7.9   | 9.1  | 10    | V    |

| IOVD                  | Overvoltage Discharge Current                                                                        | Vcc = 5V                          | 150   | 200  | 250   | mA   |

| tocp                  | OCP Deglitch Time (Note 10)                                                                          | _                                 |       | 30   |       | ms   |

| tRESTART_INTERVAL_SCP | Restart Interval Time under SCP (Note 10)                                                            | _                                 |       | 0.8  |       | s    |

| Тотр                  | Internal OTP Temperature (Note 10)                                                                   | _                                 |       | +140 |       | °C   |

| OTP EXTERNAL          | External OTP Current                                                                                 | _                                 | 90    | 100  | 110   | μA   |

| THYS                  | OTP Recovery Hysteresis Temperature<br>(Note 10)                                                     | —                                 |       | +25  | _     | °C   |

| <b>t</b> SLEEP        | Enter Sleep Mode Time after Cable<br>Detached (Note 10)                                              | _                                 | _     | 3    | _     | s    |

| tov_delay             | Delay from OVP Threshold Trip to nMOS<br>Gate Turn-Off (Note 10)                                     | —                                 | —     | —    | 50    | μs   |

| tuv_delay             | Delay from UVP Threshold Trip to nMOS<br>Gate Turn-Off (Note 10)                                     | —                                 |       | 30   | —     | ms   |

| CC1/CC2, DP/DN PIN    |                                                                                                      |                                   |       |      |       |      |

| Vl_rd3a               | Low-Voltage Threshold Used to<br>Distinguish R <sub>D</sub> Attached or Detached for<br>3A Delivery  | _                                 | _     | 1.35 | _     | V    |

| Vh_rd3a               | High-Voltage Threshold Used to<br>Distinguish R <sub>D</sub> Attached or Detached for<br>3A Delivery | _                                 | _     | 2.0  | _     | V    |

| I <sub>RD3A</sub>     | CC1/CC2 Current Source for 3A<br>Advertisement                                                       | V <sub>CC</sub> = 5V              | 304   | 330  | 356   | μA   |

| Vovp_dn               | DN Line Overvoltage Protection Threshold                                                             |                                   | 4.1   | 4.5  | 4.8   | V    |

| Vovp dp               | DP Line Overvoltage Protection Threshold                                                             | _                                 | 4.1   | 4.5  | 4.8   | V    |

7. Cable compensation voltage can be adjusted by setting from 0 to  $V_{CABLE * N}$  (N: 0 to 7). Notes:

8. 120% OVP setting & 76% UVP setting.

9. OVP blanking time during  $V_0$  transition from high output voltage to low output voltage, such as 9V to 5V, or 12V to 5V. 10. Guaranteed by design.

### **Performance Characteristics**

#### AP43771V Overview

The AP43771V is a protocol controller integrated with 8-bit 1T 8051 compatible MCU. It is compliant with the USB Power Delivery (PD) specification Rev3.0 supporting full range of Programmable Power Supply (PPS) up to 21V. It also supports USB BC1.2 and covers quick charger protocols which are implemented by High Voltage Dedicated Charging Port (HVDCP).

#### System Power-On Sequence

Once provided an external power source, the AP43771V will wake up, and the USB PD controller and MCU will be initialized. All analog control blocks will be ready and waiting for the PD negotiation process. Meanwhile, the AP43771V monitors the voltage and current conditions to avoid abnormal conditions from happening. Once any unacceptable condition happens, the AP43771V will go into the protection procedure according to the types of abnormal conditions.

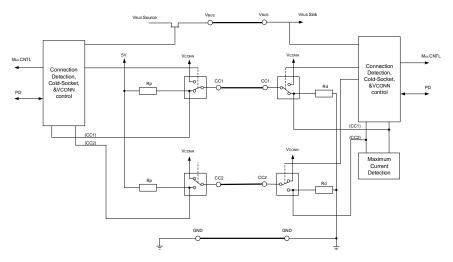

#### CC Logic and VCONN Switch

For the USB Type-C solution, two pins on the connector, CC1 and CC2, are used to establish and manage the Source-to-Sink connection, as shown in Figure 3. The CC1/CC2 voltage will be changed due to the resistor loading effect of source Rp / current source and sink Rd during the cable insertion. The AP43771V can then detect the voltage range and decide if the cable is attached, detached, or e-Marker embedded.

Once the cable is connected, both parties will negotiate which side will act as a Source or Sink by periodically changing the impedance on CC pin. The Source side will assign a pullup resistor / current source on its CC pin, and the Sink side will connect a pulldown resistor on CC pin. The AP43771V in this application will play as a Source to offer power to the Sink device, so a pullup resistor / current source is assigned on the CC pin. After the Source to Sink connection is built up, and the V<sub>CONN</sub> switch is turned on by Source to feed power to the cable through unconnected CC pin as well. At the same time, the Type-C plug orientation can be detected by monitoring the voltage on CC pins (CC1 or CC2), and then the data path from Source to Sink is accomplished.

After the attachment, the VBUS can be supplied 5V power from Source by turning on the VBUS switch, and its current capability is assigned by the pullup resistor / current source on its CC pin.

Figure 3. The USB Type-C CC Logic and VCONN Switch

#### USB Power Delivery (PD) and Phy

The AP43771V supports PD communication over USB Type-C CC channel for advanced power delivery negotiation. A USB PD physical layer that consists of pair of transmitter and receiver for Biphase Marked Coding (BMC) packet communication are embedded.

The transmitter functions include receiving packet data from the protocol layer, calculating a CRC and appending, BMC encoding, packetizing and transmitting on the CC channel. The receiver functions perform clock recovering from pre-amble, packet start detecting, BMC decoding, packet data recovering, CRC validating, packet delivering to the protocol layer or dropping.

The AP43771V is compliant with the USB Power Delivery (PD) specification Rev3.1 supporting full range of Programmable Power Supply (PPS) up to 21V. It has been certified with USB IF TID: 4305.

#### USB BC1.2 and HVDCP Protocols

The AP43771V supports USB Battery Charging Rev. 1.2 (BC1.2) and can cover High Voltage Dedicated Charging Port (HVDCP) Qualcomm QC2.0/3.0/4/4+/5 protocols to improve the charging speed between a mobile device and an adapter. The HVDCP leverages BC1.2 compliant signaling and can negotiate voltage and current request through DN/DP pin of USB connector. Meanwhile, some other popular protocols which use the same HVDCP mechanism like AFC, FCP and SCP are also available.

The AP43771V embeds the dedicated hardware to support HVDCP and can perform a better characteristic during the protocol handshaking for quick charging.

#### **Voltage Transition**

According to USB PD's protocol, the PD device requests different power profiles, and the AP43771V's power control blocks will change voltage and current values. The AP43771V provides corresponding Overvoltage Protection (OVP), Overcurrent Protection (OCP) scheme, and feedback system stability to guarantee monotonic voltage transition and avoid violating USB PD electrical specification.

The AP43771V provides zero-mismatch voltage methodology that is more flexible for customer system-design requirements. When UFP/DFP makes an acceptable power request deal, the AP43771V will change the VFB pin voltage according to the USB PD command. The voltage regulator control loop regulates the required V<sub>BUS</sub> voltage according to V<sub>FB</sub>. In addition, the shunt regulator is built-in to minimize the total external components and cost.

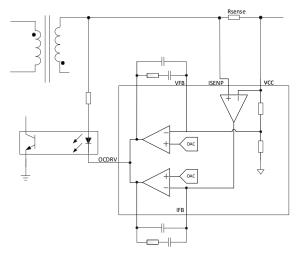

#### **CV/CC** Control Loop

The AP43771V uses Constant Voltage (CV) and Constant Current (CC) functions to control the output voltage and current as shown in Figure 4, where both loops are connected at OCDRV pin, and the feedback signal is photo-coupled from the PD controller to the primary power stage.

The CV loop regulates the output to be the expected voltage by sensing VCC through resistor divider to VFB and comparing it with a predetermined voltage set by a DAC converter. The signal difference drives OCDRV to control a photo coupler to the power stage, and then a negative feedback loop is accomplished to regulate VCC to the expected voltage. Here the DAC is used to set the expected VCC output voltage.

The CC loop controls the output to be the expected constant current by sensing the I\*Rsense drop on voltage output and comparing IFB with a predetermined voltage set by a DAC converter. The signal difference drives OCDRV to control a photo coupler to the power stage, and then a negative feedback loop is completed to adjust the I\*Rsense drop to be equal to the DAC setting. Thereby the corresponding constant current is obtained.

Figure 4. The CC/CV Control Loop in AP43771V

#### VBUS nMOS Switch Control

The built-in charge-pump circuit generates a high-voltage gate driver (PWR\_EN) to drive an external low cost high-side nMOS switch. A small resistance (10Ω) is suggested to connect the PWR\_EN to the nMOS gate. Once the PDO (Power Data Object) negotiations have matched each other between source side and sink side, PWR\_EN enables the nMOS switch and VBUS output is enabled. Otherwise, the nMOS switch will remain off. Meanwhile, during the normal operation of AP43771V, the nMOS switch is also used for power protection. Once power protection happens, the nMOS switch is turned off to protect the electrical appliances from possible damage. Meanwhile, it provides internal discharge path at VBUS pin to reduce the abnormal duration.

#### **Discharge Path**

To meet the timing requirements of the USB PD specification and field experience, the AP43771V supports the discharge paths (around 200mA sink) for VBUS pin and VCC pin to speed up the voltage drop time during PDO voltage transition, cable detaching, and power protection.

#### **ADC Converter**

The AP43771V supports an 8-bit successive approximation ADC. The input to the ADC is an analog input mux that supports multiple inputs from various voltage and current sources in the device. The output from the ADC is available to be read and used by the embedded MCU firmware. Through the data processing and appropriate algorithm, the smart controls and power protections for the AP43771V-embedded system come out.

#### Overall Features of Dedicated Part Number AP43771VFBZ-13-FR01

The AP43771VFBZ-13-FR01 is designed with standard firmware, preloaded 8 power profiles, where system manufacturers could field select a desired one through a corresponding resistor attached to the OTP pin to meet output profile requirements of a PD3.1 charger. Not only does this approach save OTP (One-Time-Programmable) programming cost, but it also greatly simplifies inventory management of PD decoder chips for various output power chargers. Meanwhile, it supports comprehensive safety protection schemes with standard receptacle output or captive cable. AP43771VFBZ-13-FR01 is available in W-DFN3030-14 (Type A1) package.

#### PDO Profile Selection and Protocol Supported (For AP43771VFBZ-13-FR01 Only)

There are a total of 8 preloaded Power profiles in the OTP memory of the AP43771VFBZ-13-FR01, illustrated in Table 1. By attaching a proper resistor with corresponding value and 1% accuracy for a desired power profile, system designers could field customize the AP43771VFBZ-13-FR01 to fit 20W to 96W different PD output power applications. Both the fixed PDO up to 20V and full range PPS with power limited mode are supported. In addition, the non-PD protocols like BC1.2, QC2.0, and other popular High Voltage Dedicated Charging Port (HVDCP), like AFC, FCP and SCP are available.

| Power<br>Profiles |       |              | USB PD PDO &   |           | Non-PD P<br>Configu | Selection<br>Resistance<br>(Ω, 1%) |         |         |              |

|-------------------|-------|--------------|----------------|-----------|---------------------|------------------------------------|---------|---------|--------------|

| 4                 | 20W   | 5V/3A        | 9V/2.22A       | 12V/1.67A | —                   | —                                  | QC 18W  | FCP 20W | 100k         |

| I                 | 2000  | 3.3V~5.9V/3A | 3.3V~11V/2.2A  | _         | —                   | —                                  | AFC 18W | SCP 20W | TUUK         |

| 2                 | 25W   | 5V/3A        | 9V/2.77A       | 12V/2.08A | —                   | —                                  | QC 18W  | FCP 25W | 82k          |

| 2                 | 2300  | 3.3V~5.9V/3A | 3.3V~11V/2.75A | _         | —                   | —                                  | AFC 18W | SCP 25W | 02K          |

| 3                 | 2014/ | 5V/3A        | 9V/3A          | _         | 15V/2A              | 20V/1.5A                           | QC 27W  | FCP 30W | 66k          |

| 3                 | 30W   |              | 3.3V~11V/3A    | _         | 3.3V~16V/2A         | —                                  | AFC 27W | SCP 30W | 00K          |

| Α                 | 30W   | 5V/3A        | 9V/3A          | 12V/2.5A  | —                   | —                                  | QC 27W  | FCP 30W | 52k          |

| 4                 | 3000  | 3.3V~5.9V/3A | 3.3V~11V/3A    | _         | —                   | _                                  | AFC 27W | SCP 30W | JZK          |

| 5                 | 2514/ | 5V/3A        | 9V/3A          | _         | 15V/2.33A           | 20V/1.75A                          | QC 27W  | FCP 35W | 2014         |

| 5                 | 35W   | _            | 3.3V~11V/3A    | _         | 3.3V~16V/2.3A       | —                                  | AFC 27W | SCP 35W | 39k          |

| 0                 | 4514/ | 5V/3A        | 9V/3A          | _         | 15V/3A              | 20V/2.25A                          | QC 27W  | FCP 45W | 001          |

| 6                 | 45W   | —            | 3.3V~11V/4.05A | _         | 3.3V~16V/3A         | —                                  | AFC 27W | SCP 45W | 26k          |

| 7                 | CEN/  | 5V/3A        | 9V/3A          | —         | 15V/3A              | 20V/3.25A                          | QC 27W  | FCP 60W | 454          |

| /                 | 65W   | _            | _              | _         | 3.3V~16V/4.05A      | 3.3V~21V/3.25A                     | AFC 27W | SCP 60W | 15k          |

| 0                 | 0014/ | 5V/5A        | 9V/5A          | _         | 15V/5A              | 20V/4.8A                           | QC 27W  | FCP 60W | <b>5</b> 41. |

| 8                 | 96W   | —            | <u> </u>       | _         | 3.3V~16V/5A         | 3.3V~21V/5A                        | AFC 27W | SCP 60W | 5.1k         |

#### Table 1. Power Profile Selection Table

Notes: 11. All profiles support cable 90mΩ resistance compensation, DCP mode in 5V/3A, and Apple mode in 5V/3A.

12. All PPS profiles are set at power limited mode.

13. AFC mode is supported and is the same with QC mode.

14. FCP mode and SCP mode are supported up to 60W.

15. Overvoltage protection (OVP) is set at 120% of PDO output.

16. Undervoltage protection (UVP) is set at 75% of PDO output.

17. Short-circuit protection (SCP) is set at  $0\Omega$  load.

18. Overcurrent protection (OCP) is set at 110% of maximum load for fixed PDO, DCP and Apple modes, while constant-current protection is used in PPS, QC, AFC, FCP and SCP modes.

19. Vendor ID (VID) = 10817 is assigned in VDM command.

20. It is suggested to use 1% accuracy of selection resistance. If the resistor is left open or short, the power profile is set to 20W or 96W respectively.

#### Power Protection Configuration (For AP43771VFBZ-13-FR01 Only)

The AP43771VFBZ-13-FR01 provides OVP/UVP/OCP/SCP power protection functions and also supports Constant Current (CC) function in PPS operation and other constant current modes. All of the protection thresholds are related to the requested power profile.

The OVP threshold is set at 120% of PDO output. Once the VBUS output voltage is higher than OVP threshold, the VBUS MOS is turned off and an internal discharge path from VBUS pin to ground to reduce the overvoltage duration.

The UVP threshold is set at 75% of PDO output. Once the VBUS output voltage drops to UVP threshold, the VBUS MOS is turned off to avoid the abnormal operation of the electrical appliances.

The OCP threshold is set at 110% of PDO maximum load for fixed PDO, DCP, and Apple modes. Once the VBUS output current is higher than OCP threshold, the AP43771VFBZ-13-FR01 will shut down VBUS output and send out "Hard Reset" command to the Sink device. For the PPS, QC, AFC, FCP, and SCP, the constant-current (CC) protection is used. Once the output current exceeds the allowed maximum current, the output voltage will drop sharply and trigger the UVP to turn off the VBUS output. When the output voltage drops below UVLO threshold, the AP43771VFBZ-13-FR01 will reset.

For the SCP power protection, it is triggered as soon as both the OCP and UVP happen. It is set with 0Ω load used.

#### Captive Cable Support Configuration (For AP43771VFBZ-13-FR01 Only)

The AP43771VFBZ-13-FR01 supports adapter with receptacle or captive cable. If captive cable is selected, the 8.5kΩ resistor should be connected from CC2 pin to ground, as shown in Figure 5 below.

Figure 5. Captive Cable Is Supported Through a Resistor Connection from CC2 Pin to Ground

#### I2C Interface (W-QFN4040-24 (Type A1) Only, for Customized Firmware Only)

To support multiple Type-C ports PD applications, the AP43771V (W-QFN4040-24 (Type A1)) can be used for implementing smart power sharing scheme. One AP43771V works as a Master to monitor status of other Slave AP43771V through I2C interface. The Master AP43771V can deliver I2C commands to the Slave AP43771V for re-allocating desired power profile for each Type-C port.

Due to the complicated conditions and diversified requirements in Multiple ports application, the power sharing function needs to be implemented with customized firmware.

AP43771V includes I2C Interface pins (SCL, SDA,) as below table shows, and I2C commands are supported by firmware so that It can monitor and change status of other I2C devices.

| I2C Interface F | Pin List |

|-----------------|----------|

|-----------------|----------|

| Pin No | Pin Name | Pin Function |

|--------|----------|--------------|

| 4      | SDA      | I2C Data     |

| 5      | SCL      | I2C Clock    |

One AP43771V plays as an I2C either master or slave device. The I2C read and write operations are supported as below.

All transactions begin with a START (S) and be terminated by a STOP (P). A START condition is defined whenever a HIGH to LOW transition on the SDA while SCL is HIGH. A STOP condition is defined whenever a LOW to HIGH transition on the SDA while SCL is HIGH. START and STOP conditions are always generated by the master.

I2C Format for Write Data

| S | Sla | ve Address | W | А | (CMD)Address | А |   | Data 0 | А | ⇒ |

|---|-----|------------|---|---|--------------|---|---|--------|---|---|

|   | >   | Data       |   | А | Data n       | А | Ρ |        |   |   |

|   |     |            |   |   |              |   |   |        |   |   |

I2C Format for Read Data

| S | Sla | ve Address | W | А | (CMD)Address | А | Ρ |   | S     | Slave Addre | ss | R | А | ⇒ |

|---|-----|------------|---|---|--------------|---|---|---|-------|-------------|----|---|---|---|

|   | ⇒   | Data 0     |   | А | Data         | А |   | D | ata n | NA P        |    |   |   |   |

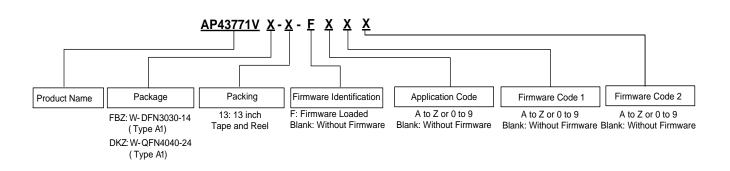

## **Ordering Information**

| Orderable Part Number | Deekere                   | Identification | Firmware Inside                                           | Packing |                 |  |

|-----------------------|---------------------------|----------------|-----------------------------------------------------------|---------|-----------------|--|

| (Note 21)             | Package                   | Code           | Firmware inside                                           | Qty.    | Carrier         |  |

| AP43771VFBZ-13-FR01   | W-DFN3030-14              | 4V             | Standard Firmware<br>(Function as described in Datasheet) |         |                 |  |

| AP43771VFBZ-13-FXXX   | (Type A1)                 | - V            | Customized Firmware                                       | 3000    | 13" Tape & Reel |  |

| AP43771VDKZ-13-FXXX   | W-QFN4040-24<br>(Type A1) | 6B             | Customized Firmware                                       |         |                 |  |

Note: 21. It is recommended to order Standard Firmware device based on functions described in datasheet. For without firmware and customized options, please contact us or your local Diodes representative.

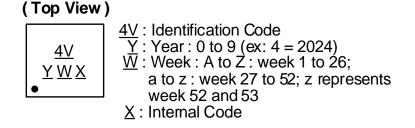

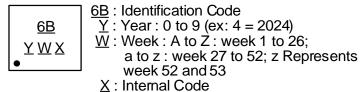

### **Marking Information**

#### W-DFN3030-14 (Type A1)

#### W-QFN4040-24 (Type A1)

### (Top View)

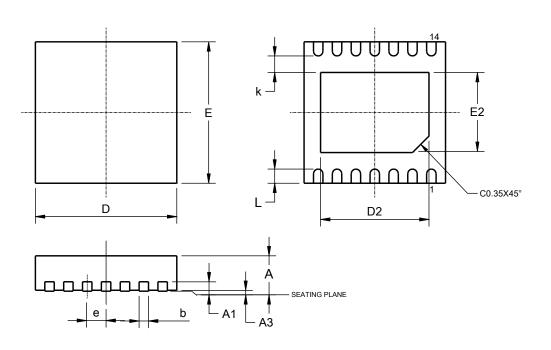

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

| v     | W-DFN3030-14<br>(Type A1) |             |      |  |  |  |  |  |  |  |  |

|-------|---------------------------|-------------|------|--|--|--|--|--|--|--|--|

| Dim   | Min                       | Min Max Typ |      |  |  |  |  |  |  |  |  |

| Α     | 0.70                      | 0.80        | 0.75 |  |  |  |  |  |  |  |  |

| A1    | 0                         | 0.05        | 0.02 |  |  |  |  |  |  |  |  |

| A3    | 0                         | .203RE      | F    |  |  |  |  |  |  |  |  |

| b     | 0.15                      | 0.25        | 0.20 |  |  |  |  |  |  |  |  |

| D     | er)                       | 8.00BS      | 0    |  |  |  |  |  |  |  |  |

| D2    | 2.55                      | 2.65        | 2.60 |  |  |  |  |  |  |  |  |

| е     | C                         | .40BS       | 0    |  |  |  |  |  |  |  |  |

| Е     | 9                         | .00BS       | 0    |  |  |  |  |  |  |  |  |

| E2    | 1.65                      | 1.75        | 1.70 |  |  |  |  |  |  |  |  |

| k     | 0.20                      |             |      |  |  |  |  |  |  |  |  |

| L     | 0.35                      | 0.45        | 0.40 |  |  |  |  |  |  |  |  |

| All D | imens                     | ions in     | mm   |  |  |  |  |  |  |  |  |

W-DFN3030-14 (Type A1)

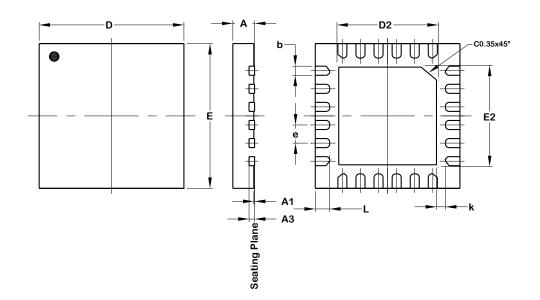

W-QFN4040-24 (Type A1)

| W-QFN4040-24         |           |      |      |  |

|----------------------|-----------|------|------|--|

| (Type A1)            |           |      |      |  |

| Dim                  | Min       | Max  | Тур  |  |

| Α                    | 0.70      | 0.80 | 0.75 |  |

| A1                   | 0.00      | 0.05 | 0.02 |  |

| A3                   | 0.203 REF |      |      |  |

| b                    | 0.18      | 0.30 | 0.25 |  |

| D                    | 4.00 BSC  |      |      |  |

| D2                   | 2.65      | 2.75 | 2.70 |  |

| Е                    | 4.00 BSC  |      |      |  |

| E2                   | 2.65      | 2.75 | 2.70 |  |

| е                    | 0.50 BSC  |      |      |  |

| k                    | 0.20      |      |      |  |

| L                    | 0.35      | 0.45 | 0.40 |  |

| All Dimensions in mm |           |      |      |  |

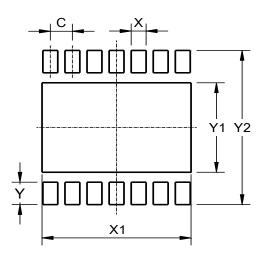

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

| Dimensions | Value (in mm) |  |

|------------|---------------|--|

| С          | 0.40          |  |

| Х          | 0.27          |  |

| X1         | 2.70          |  |

| Y          | 0.45          |  |

| Y1         | 1.80          |  |

| Y2         | 3.10          |  |

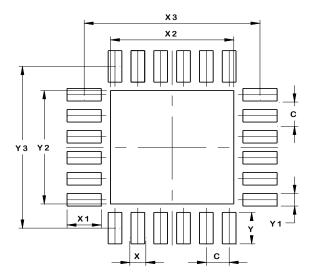

#### W-QFN4040-24 (Type A1)

W-DFN3030-14 (Type A1)

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.500            |

| Х          | 0.300            |

| X1         | 0.750            |

| X2         | 2.700            |

| X3         | 3.850            |

| Y          | 0.750            |

| Y1         | 0.300            |

| Y2         | 2.700            |

| Y3         | 3.850            |

### **Mechanical Data**

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per J-STD-202 (3)

- Weight:

- W-DFN3030-14 (Type A1): 0.017 grams (Approximate)

- W-QFN4040-24 (Type A1): 0.041 grams (Approximate)

#### **IMPORTANT NOTICE**

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<u>https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</u>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com