### **PAM8965**

12W STEREO CLASS-D AUDIO AMPLIFIER WITH SYNCHRONOUS BOOST, SSM AND EXTERNAL AUDIO FEEDBACK

### Description

The PAM8965 is an extremely high-efficiency Class-D stereo audio power amplifier with an integrated synchronous boost converter. The PAM8965 can drive two channels with 12W each into  $4\Omega$  speakers.

The integrated amplifier can achieve system efficiency of 92% (at  $V_{BAT} = 7.4V$ ). The device consumes exceptionally low quiescent current (10mA at  $V_{BAT} = 7.4V$ ) and very low shutdown current (0.7µA).

The integrated current-mode boost converter provides regulated power to a feature-laden Class-D stereo amplifier. These include:

Spread spectrum modulation (SSM) for EMI suppression (audio and boost), which enables the use of inexpensive ferrite bead filters.

Non-clipping power limit, which uses 41-step automatic gain control.

Thermal foldback, which reduces output power as the chip heats up.

External audio feedback pins, which allow for customization of sound by using feedback network design. Alternatively, these pins can be used for Kelvin connection to speaker terminals.

GAIN pin to program audio gain at 0.5dB steps such that external resistors are not required to adjust gain, which can result in gain error.

Out-of-audio switching for the boost converter, which minimizes audible noise coming from components on the board.

Protection features include undervoltage and overvoltage protection on VBAT, overvoltage protection on PVDD, short-circuit protection on all audio outputs, cycle-by-cycle current limit on boost converter, thermal shutdown of the entire system, DC protection for speakers, and an FLT pin that provides a fault flag.

### Features

- Operates from 2.8V to 8.5V Supply

- $2 \times 12W$  (10% THD+N) into  $4\Omega$  Load with V<sub>BAT</sub> = 7.4V (2SxP)

- $2 \times 8W$  (10% THD+N) into 6 $\Omega$  Load with V<sub>BAT</sub> = 3.7V (1SxP)

- Auto Gain Control Responds to:

- Thermal Foldback

- Non-Clip Power Limit

- GAIN Pin

- Externally Adjustable Gain from 26dB to 6dB with 0.5dB Steps

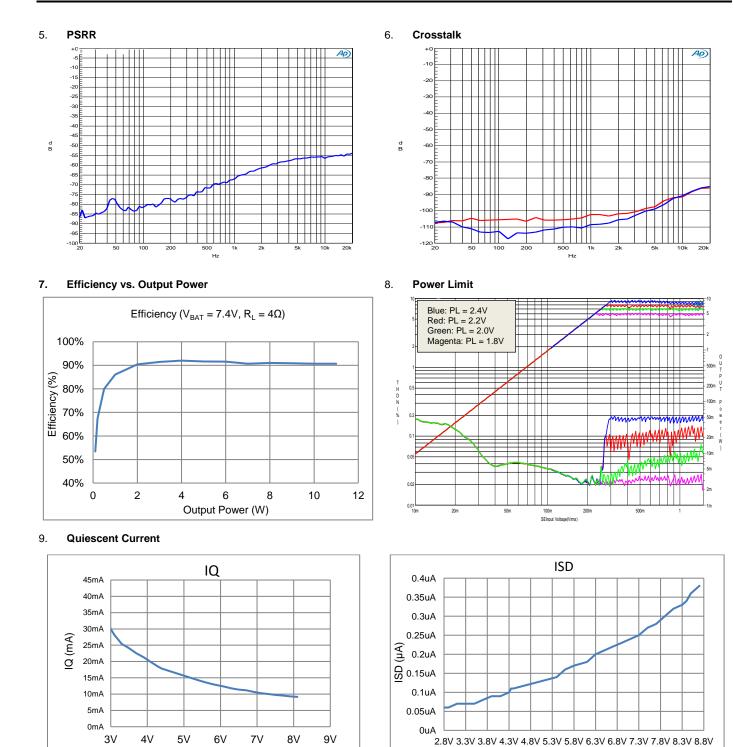

- Exceptionally High Overall System Efficiency (92% @ V<sub>BAT</sub> = 7.4V)

- Very Low Iq = 10mA (VBAT = 7.4V) for Boost + Stereo

- Very Low Shutdown Current = 0.7µA

- DC Protection for Speaker

- Auto-Recovery on Short-Circuit Protection & Thermal Shutdown

- External Audio Feedback Pins

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. https://www.diodes.com/guality/product-definitions/

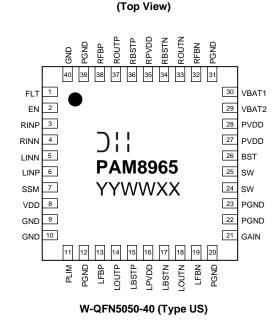

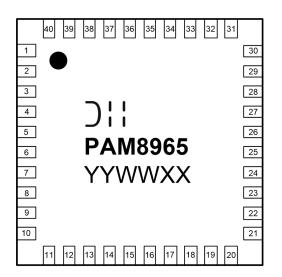

### **Pin Assignments**

### Applications

- Portable electronics

- **Bluetooth speakers**

- Wireless speakers

- Music instruments

- High-capacitance piezo actuator drives

- Virtual reality 3D active feedbacks

- PDAs, GPS, game machines

- Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and

- Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

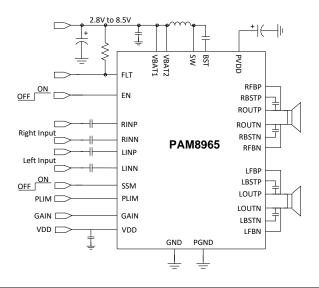

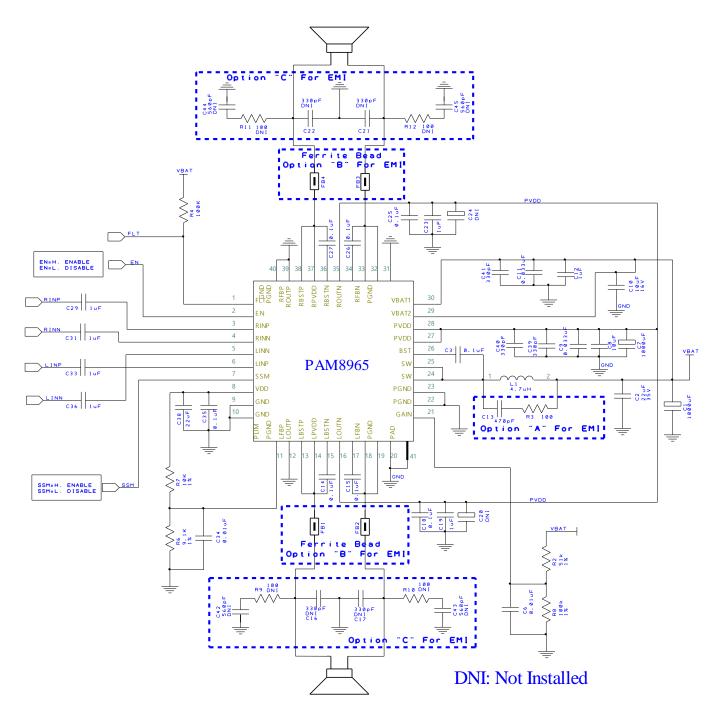

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number | Pin Name | I/O/P    | Description                                                                                                            |

|------------|----------|----------|------------------------------------------------------------------------------------------------------------------------|

| 1          | FILT     | 0        | Fault flag. Open-drain output to signal system faults (VBAT UVLO or OVLO, OTP, DC input, audio SCP)                    |

| 2          | EN       | <u> </u> | Chip enable. High = ON, Low = OFF. Do not float this pin.                                                              |

| 3          | RINP     |          | Right channel audio input – Positive                                                                                   |

| 4          | RINN     | 1        | Right channel audio input – Negative                                                                                   |

| 5          | LINN     |          | Left channel audio input – Negative                                                                                    |

| 6          | LINN     |          | Left channel audio input – Negative                                                                                    |

| 7          | SSM      |          | Spread spectrum modulation. High = ON, Low = OFF. Do not float this pin.                                               |

| 8          | VDD      | 0        | Internal 5V LDO                                                                                                        |

| -          | GND      | 0        |                                                                                                                        |

| 9, 10      |          | -        | Analog signal ground                                                                                                   |

| 11         | PLIM     | I        | Non-clip power limit setting. PLIM = VDD disables power limit. Do not float this pin.                                  |

| 12, 20     | PGND     |          | Power ground for left channel                                                                                          |

| 13         | LFBP     |          | Left channel feedback – Positive. Short to LOUTP. Kelvin connect to speaker for higher performance.                    |

| 14         | LOUTP    | 0        | Left channel audio output – Positive                                                                                   |

| 15         | LBSTP    | Р        | Left channel boot-strap supply for high-side – Positive                                                                |

| 16         | LPVDD    | Р        | Left channel power supply for Class-D H-bridge                                                                         |

| 17         | LBSTN    | Р        | Left channel boot-strap supply for high-side – Negative                                                                |

| 18         | LOUTN    | 0        | Left channel audio output – Negative                                                                                   |

| 19         | LFBN     | Ι        | Left channel feedback – Negative. Short to LOUTN. Kelvin connect to speaker for higher performance.                    |

|            |          |          | Audio channel gain setting. Do not float this pin.                                                                     |

| 21         | GAIN     | I        | 4.5V or above = 26dB (maximum gain setting).<br>Then every 100mV is 0.5dB step, e.g., 4.4V = 25.5dB, 4.3V = 25dB, etc. |

|            |          |          | 0.5V or below = 6dB (minimum gain setting)                                                                             |

| 22, 23     | PGND     | _        | Power ground for boost converter                                                                                       |

| 24, 25     | SW       | 0        | Boost converter's switching node                                                                                       |

| 26         | BST      | P        | Boost converter's boot-strap supply                                                                                    |

| 27, 28     | PVDD     | 0        | Boost converter's output. Connect this to pin 16 and pin 35.                                                           |

| 29         | VBAT2    | P        | Battery supply input for boost converter. See Application Information for decoupling requirement.                      |

| 30         | VBAT1    | P        | Battery supply input for system. See Application Information for decoupling requirement.                               |

| 31, 39     | PGND     |          | Power ground for right channel                                                                                         |

| 32         | RFBN     | 1        | Right channel feedback – Negative. Short to ROUTN. Kelvin connect to speaker for higher performance.                   |

| 33         | ROUTN    | 0        | Right channel audio output – Negative                                                                                  |

| 34         | RBSTN    | P        | Right channel boot-strap supply for high-side – Negative                                                               |

| 35         | RPVDD    | P        | Right channel power supply for Class-D H-bridge                                                                        |

| 36         | RBSTP    | P        | Right channel boot-strap supply for high-side – Positive                                                               |

| 37         | ROUTP    | 0        | Right channel audio output – Positive                                                                                  |

| 38         | RFBP     | -        | Right channel feedback – Positive. Short to ROUTP. Kelvin connect to speaker for higher performance.                   |

| 40         | GND      |          | Connect to system ground                                                                                               |

PAM8965

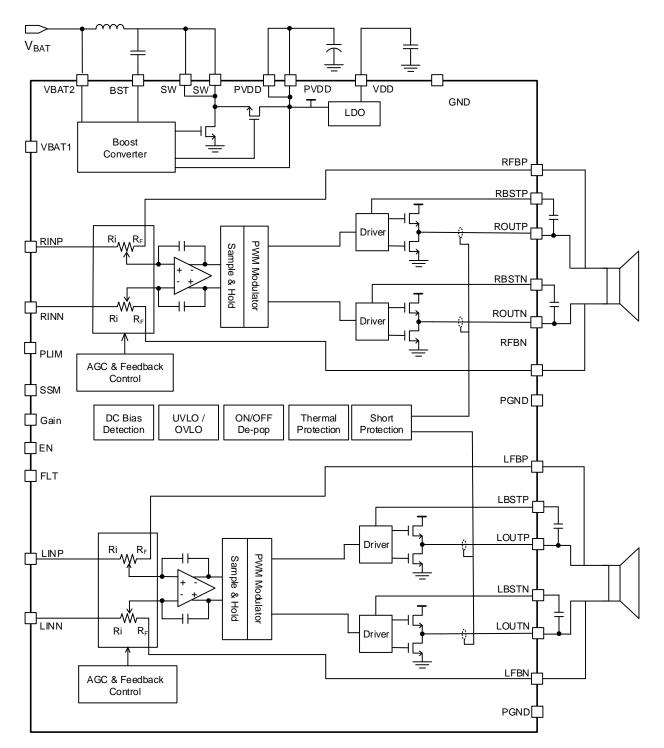

# **Functional Block Diagram**

Figure 1. PAM8965 Block Diagram

### Absolute Maximum Ratings (@T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 4)

| Symbol                         | Parameter                                       | Rating                                        | Unit |

|--------------------------------|-------------------------------------------------|-----------------------------------------------|------|

| VBAT                           | Supply Voltage (Pins VBAT1, VBAT2)              | -0.3 to +9.0                                  | V    |

| VRINP, VRINN, VLINP, VLINN     | Audio Input Voltage                             | -0.3 to +5.5                                  | V    |

| Vplim, Vgain, Vssm             | Control Input Voltage                           | -0.3 to +6.0                                  | V    |

| Ven                            | Control Input Voltage                           | -0.3 to V <sub>BAT</sub>                      | V    |

| Vsw                            | Boost Switching Voltage                         | -2 to +16 (within 10ns)<br>-0.3 to +10.2 (DC) | V    |

| Vpvdd, Vlpvdd, Vrpvdd          | Boost Output Voltage                            | -0.3 to +10.2 (DC)                            | V    |

| Vloutp, Vloutn, Vroutp, Vroutn | Class D Output Voltage                          | -1 to +12 (within 10ns)<br>-1 to +10.2 (DC)   | V    |

| Tj_max                         | Maximum Operating Junction Temperature (Note 5) | -40 to +150                                   | °C   |

| Tstg                           | Storage Temperature Range                       | -40 to +150                                   | °C   |

| HBM                            | ESD (Human Body Model)                          | ±2000                                         | V    |

| CDM                            | ESD (Charged Device Model)                      | ±1000                                         | V    |

Notes: 4. Stresses greater than the Absolute Maximum Ratings specified above can cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability can be affected by exposure to Absolute Maximum Ratings conditions for extended periods of time.

5. The PAM8965 incorporates an exposed thermal pad on the underside of the chip, which acts as a heatsink. The exposed pad must be connected to a thermally dissipating Cu plane on the PCB for adequate power dissipation. Failure to do so may result in the device going into thermal shutdown.

### Recommended Operating Conditions (@TA = +25°C, unless otherwise specified.)

| Symbol                                                       | Parameter                                         | Min | Max  | Unit |

|--------------------------------------------------------------|---------------------------------------------------|-----|------|------|

| VBAT                                                         | Supply Voltage (Pins VBAT1, VBAT2)                | 2.8 | 8.5  | V    |

| VRINP, VRINN, VLINP, VLINN                                   | Audio Input Voltage                               | 0.0 | 5.0  | V    |

| Vplim, Vgain, Vssm                                           | Control Input Voltage                             | 0.0 | 5.5  | V    |

| VEN                                                          | Control Input Voltage                             | 0.0 | VBAT | V    |

| <b>D</b> i unu                                               | Minimum Load Resistance (V <sub>BAT</sub> ≤ 5.0V) | 6   | _    | 0    |

| R <sub>LMIN</sub>                                            | Minimum Load Resistance (VBAT > 5.0V)             | 4   | _    | Ω    |

| TA                                                           | Operating Free-Air Temperature Range              |     | +85  | °C   |

| T <sub>J</sub> Operating Junction Temperature Range (Note 5) |                                                   | -40 | +125 | °C   |

### **Thermal Information**

| Parameter                                | Symbol | Package                | Rating | Unit |

|------------------------------------------|--------|------------------------|--------|------|

| Thermal Resistance (Junction to Ambient) | θ」Α    | W-QFN5050-40 (Type US) | 33     | °C/W |

| Thermal Resistance (Junction to Case)    | θJC    | W-QFN5050-40 (Type US) | 10     | °C/W |

| Symbol            | Parameter                           | Test Condition                                              | Min  | Тур   | Мах  | Unit |  |

|-------------------|-------------------------------------|-------------------------------------------------------------|------|-------|------|------|--|

| VBAT              | Input Supply Voltage                | _                                                           | 2.8  | _     | 8.5  | V    |  |

| Vih               | High-Level Input Voltage            | EN, SSM                                                     | 1.5  | _     | _    | V    |  |

| VIL               | Low-Level Input Voltage             | EN, SSM                                                     | _    | _     | 0.5  | V    |  |

|                   | System Efficiency (Depart + Stores) | $V_{BAT}$ = 7.4V, $R_L$ = 4 $\Omega$ , $P_O$ = 5W, f = 1kHz | _    | 92    |      | 0/   |  |

| η                 | System Efficiency (Boost + Stereo)  | $V_{BAT} = 3.7V, R_L = 6\Omega, P_O = 3W, f = 1kHz$         | _    | 86    | _    | %    |  |

|                   | V <sub>BAT</sub> = 7.4V, No Load    |                                                             | _    | 10    | _    |      |  |

| lq                | Quiescent Current                   | V <sub>BAT</sub> = 3.7V, No Load                            | _    | 20    | _    | mA   |  |

| Isd               | Shutdown Current                    | V <sub>EN</sub> = 0, V <sub>BAT</sub> = 2.8V to 8.5V        | _    | 0.7   | 5.0  | μA   |  |

|                   |                                     | VBAT Rising                                                 |      | 2.7   | 2.8  |      |  |

| UVLO              | VBAT UVLO Threshold                 | V <sub>BAT</sub> Falling                                    | 2.30 | 2.45  | 2.55 | V    |  |

|                   |                                     | Hysteresis                                                  | _    | 0.250 | _    | 1    |  |

|                   |                                     | V <sub>BAT</sub> Rising                                     | 8.6  | 8.95  | 9.2  |      |  |

| OVLO              | VBAT OVLO Threshold                 | VBAT Falling                                                | 8.5  | 8.6   | _    | V    |  |

|                   |                                     | Hysteresis                                                  | _    | 0.350 | _    |      |  |

| TSD               | Thermal Shutdown Threshold          | _                                                           | _    | +150  | _    |      |  |

| TSD_HYS           | Thermal Shutdown Hysteresis         |                                                             | _    | +40   | —    | °C   |  |

| T <sub>FOLD</sub> | Thermal Foldback Trip Point         | _                                                           | _    | +125  | _    |      |  |

# **Electrical Characteristics** (V<sub>BAT</sub> = 7.4V, T<sub>A</sub> = +25°C, R<sub>L</sub> = $4\Omega + 2 \times 33\mu$ H, V<sub>PLIM</sub> = V<sub>GAIN</sub> = V<sub>DD</sub>, unless otherwise specified.)

# **Boost Converter** ( $V_{BAT}$ = 7.4V, $T_A$ = +25°C, $R_L$ = 4 $\Omega$ + 2 × 33 $\mu$ H, $V_{PLIM}$ = $V_{GAIN}$ = $V_{DD}$ , unless otherwise specified.)

| Symbol           | Parameter                        | Test Condition   |           | Min | Тур | Max | Unit |

|------------------|----------------------------------|------------------|-----------|-----|-----|-----|------|

| Vpvdd            | Boost Output Voltage             | —                | _         |     | 9.2 | _   | V    |

|                  | Boost Switching Frequency        | —                | _         | 768 | _   | kHz |      |

| fsw              | Boost Switching Frequency in PFM | No Load          | 50        | 75  | _   | kHz |      |

|                  |                                  | Rectifier Switch | L 00-5 A  |     | 50  | _   | mΩ   |

| Ron              | On-State Resistance (Boost)      | Low-Side Switch  | I∟ = 20mA |     | 50  | _   | mΩ   |

| I <sub>LIM</sub> | Boost Converter Current Limit    | —                |           | 8   | —   | Α   |      |

## **Class-D Amplifier** (V<sub>BAT</sub> = 7.4V, T<sub>A</sub> = +25°C, R<sub>L</sub> = $4\Omega + 2 \times 33\mu$ H, V<sub>PLIM</sub> = V<sub>GAIN</sub> = V<sub>DD</sub>, unless otherwise specified.)

| Symbol           | Parameter                         | Test Condition                                               |                           |        | Тур   | Max | Unit  |  |

|------------------|-----------------------------------|--------------------------------------------------------------|---------------------------|--------|-------|-----|-------|--|

|                  | Continuous Output Power, 2SxP     | $V_{BAT}$ = 7.4V, $R_L$ = 4 $\Omega$ , f = 1kHz, THD+N = 10% |                           |        | 12.0  | —   | W     |  |

| Po               | (per Channel) (Note 6)            | $V_{BAT} = 7.4V, R_L = 4\Omega, f = 1kHz, THE$               | 0+N = 1%                  | _      | 9.6   | _   | W     |  |

| Po               | Continuous Output Power, 1SxP     | $V_{BAT} = 3.7V, R_L = 6\Omega, f = 1kHz, THE$               | 0+N = 10%                 | _      | 8.0   | _   | W     |  |

|                  | (per Channel) (Note 7)            | $V_{BAT} = 3.7V, R_L = 6\Omega, f = 1kHz, THE$               | 0+N = 1%                  | _      | 6.4   | _   | W     |  |

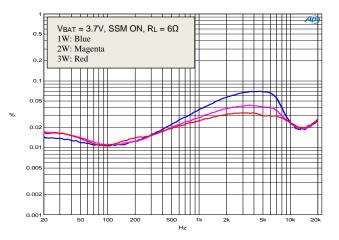

|                  |                                   | $V_{BAT} = 7.4V, R_L = 4\Omega, P_O = 5W, C_{P_V}$           | /DD = 220µF               | _      | 0.035 | _   | 0/    |  |

| THD+N            | Total Harmonic Distortion + Noise | $V_{BAT} = 3.7V, R_L = 6\Omega, P_O = 3W, C_{PV}$            | <sub>/DD</sub> = 220µF    |        | 0.023 | —   | %     |  |

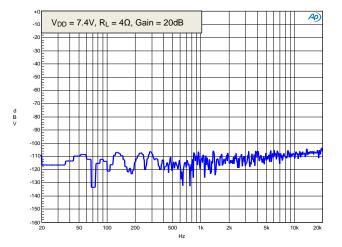

|                  |                                   | Gain = 20dB                                                  | A-Weighting               |        | 50    | —   |       |  |

|                  |                                   | VIN @ AC Ground, 20Hz to 22kHz<br>SSM Off                    | No A-Weighting            | _      | 70    | —   | μVrms |  |

| Vn               | Integrated Output Noise           | Gain = 26dB                                                  | A-Weighting               | _      | 70    | —   |       |  |

|                  |                                   | VIN @ AC Ground, 20Hz to 22kHz<br>SSM Off                    | No A-Weighting            |        | 100   | —   | ]     |  |

| DODD             | Deven Overska Delivativa Detio    | VIN = AC Ground                                              | f = 217Hz                 |        | -79   | —   | dB    |  |

| PSRR             | Power Supply Rejection Ratio      | ±100mV Supply Ripple<br>Gain = 26dB                          | f = 1kHz                  |        | -67   | —   | uв    |  |

| SNR              | Signal-to-Noise Ratio             | THD+N = 1%, Gain = 26dB,<br>A-Weighted, SSM Off              | f = 1kHz                  | _      | 100   | _   | dB    |  |

| Gv               | Gain                              | GAIN = VDD                                                   | —                         | — 26 — |       | _   | dB    |  |

| Gv               | Gain                              | GAIN = GND                                                   | —                         | _      | 6     | _   | uв    |  |

| Vos              | Output Offset Voltage             | VIN @ AC Ground, Gain = 26dB                                 | —                         | _      | 1     | 10  | mV    |  |

| fosc             | Audio Oscillator Frequency        | —                                                            | —                         | _      | 384   | —   | kHz   |  |

| Duu              | Innut Desistance                  | GAIN = VDD (26dB)                                            | —                         | _      | 15    | _   | kΩ    |  |

| Rin              | Input Resistance                  | GAIN = GND (6dB)                                             | —                         | —      | 105   | —   | K12   |  |

| ton              | Startup Time from EN Asserted     | —                                                            | —                         | _      | 15    | _   | ms    |  |

| Davi             | On State Resistance (Class D)     | High-Side H-Bridge Switch                                    | L 100mA                   | _      | 100   | —   | mΩ    |  |

| Ron              | On-State Resistance (Class-D)     | Low-Side H-Bridge Switch                                     | I∟ = 100mA                |        | 100   | _   |       |  |

| R <sub>FLT</sub> | FLT Open-Drain Resistance         | Under Any Fault Condition                                    | Under Any Fault Condition |        |       | —   | kΩ    |  |

Notes:

6. For 2SxP battery configuration, minimum speaker resistance supported is 4Ω per channel.

7. For 1SxP battery configuration, minimum speaker resistance supported is 6Ω per channel.

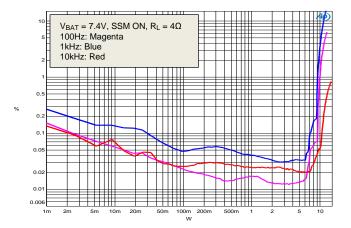

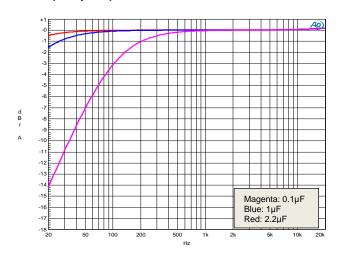

### **Performance Characteristics** ( $V_{BAT} = 7.4V$ , $T_A = +25^{\circ}C$ , $R_L = 4\Omega + 33\mu$ H, $V_{GAIN} = V_{DD}$ , SSM On, unless otherwise specified.)

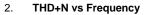

#### 1. THD+N vs Power

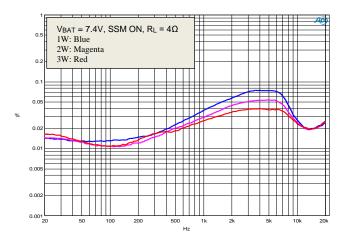

#### 3. Frequency Response

# $Performance \ Characteristics \ (V_{BAT} = 7.4V, \ T_A = +25^{\circ}C, \ R_L = 4\Omega + 33\mu H, \ V_{GAIN} = V_{DD}, \ unless \ otherwise \ specified.) \ (continued)$

VBAT (V)

VBAT (V)

# $Performance \ Characteristics \ (V_{BAT} = 7.4V, \ T_A = +25^{\circ}C, \ R_L = 4\Omega + 33 \mu H, \ GAIN = VDD, \ unless \ otherwise \ specified.)$

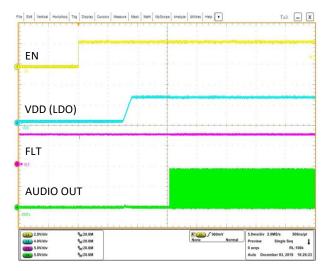

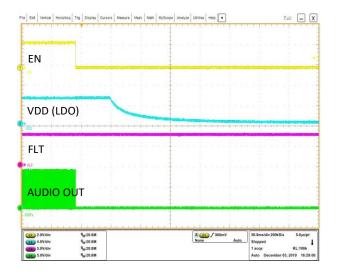

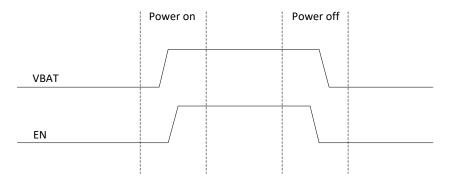

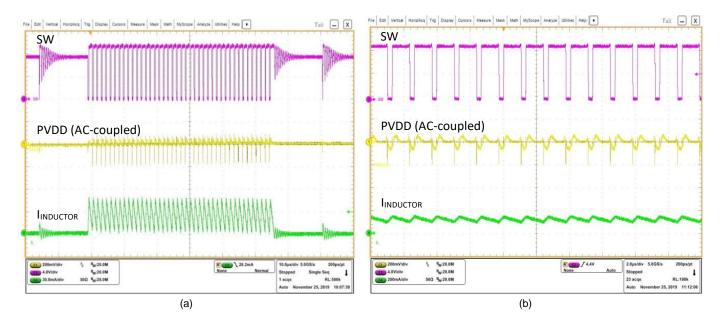

#### 10. Startup Waveform with EN Control

#### 11. Shutdown Waveform with EN Control

### **Detailed Description**

The PAM8965 is a stereo Class-D audio amplifier with integrated synchronous boost converter. The device boasts system efficiency of 92% (V<sub>BAT</sub> = 7.4V), which implies that the boost converter and stereo Class-D amplifier can reach average efficiency of 96% each, negating any advantage of using separate ICs. The high efficiency also allows PAM8965 to deliver 2 × 12W (10% THD+N with V<sub>BAT</sub> = 7.4V) in to 2 × 4 $\Omega$  speakers without the need of a heat sink.

The two Class-D audio channels, the integrated synchronous boost converter, and the high efficiency makes PAM8965 an extremely cost-effective general-purpose audio amplifier. The integration also results in the reduction of external components.

With V<sub>BAT</sub> (input power supply) range of 2.8V to 8.5V, the PAM8965 is perfectly suited for battery applications. The wide input supply range makes it ideal for 1SxP or 2SxP Li-ion battery configurations. In addition, the PAM8965 consumes just 10mA quiescent current (V<sub>BAT</sub> = 7.4V), and the shutdown current is only 0.7 $\mu$ A (typ), which helps to extend the battery life.

The synchronous boost converter provides a regulated output of 9.2V and operates in pulse width modulation (PWM) mode for medium to high load. For light load condition, the converter transitions to pulse frequency modulation (PFM) mode to improve the efficiency of the converter. In PFM mode, to avoid the switching frequency from dropping in to the audio band, the boost converter features an out-of-audio mode, which keeps the switching frequency above 75kHz (typ). This minimizes the possibility of audible vibrations coming from the components mounted on the PCB.

In terms of performance, the integrated output noise of the audio channel at maximum gain setting of 26dB is only  $70\mu$ Vrms (A-weighted). Similarly, THD+N is only 0.035% at Po = 5W. The chopper-enabled integrator in the audio channel ensures that the output offset is typically < 1mV at maximum gain.

The headlining feature of PAM8965 is the provision of external audio feedback pins. While internal feedback connection takes care of nonlinearities only in the internal feedback loop, with external feedback pins, the feedback can be Kelvin-connected to the speaker terminals. This eliminates parasitic resistance and inductance from bond wires, PCB trace, ferrite beads and long speaker leads from adversely affecting the fidelity of the audio signal. Furthermore, the external feedback pins allow the use of filter networks in the feedback path to customize sound without relying on DSP.

In terms of features, the PAM8965 incorporates a 41-step (0.5dB per step) automatic gain control (AGC) system, which delivers smooth variations in audio channel gain when responding to the following conditions:

- Junction temperature exceeds +125°C (thermal foldback)

- Output power exceeds a set threshold based on PLIM pin voltage (non-clip power limit)

- Volume control based on the GAIN pin voltage

The PAM8965 output can be driven in single-ended or in bridge-tied-load (BTL) configuration.

Spread spectrum modulation (SSM) allows the use of inexpensive ferrite bead filters and yet meet EMI specification. Although boost switching frequency (768kHz) is twice that of Class-D PWM frequency (384kHz), nevertheless, the spread added on both systems due to SSM is synchronized. This ensures audible beats are not generated due to difference in switching frequencies.

The startup time, defined as the time between EN asserted and audible output from the speakers, is only 15ms. This includes the boost converter startup and audio channel wake-up along with the pre-charge of the DC-blocking capacitors at audio Inputs. The advantage of this fast start is that the device does not require mute control. The device can be enabled when audio output is required, and disabled when audio output is off, consuming only 0.7µA in the off state.

The PAM8965 has a multitude of protection features, which include undervoltage and overvoltage lockout on VBAT, overvoltage lockout on PVDD, short-circuit protection on all audio outputs, cycle-by-cycle current limit on the boost converter, thermal shutdown of the entire system, speaker protection against DC audio, and an FLT pin that provides a fault flag.

### **Application Information**

#### Audio Input

The PAM8965 supports differential and single-ended input configurations.

#### **Differential Input**

Differential input operation minimizes noise that appears common on both the input lines of the channel. To apply a differential input, connect the positive terminal of the audio source to xINP pin and connect the negative terminal to xINN pin, where x can be L or R for Left and Right channels, respectively.

It is best to AC-couple the audio source to xINP and xINN pins.

#### Single-Ended Input

To apply a single-ended input, connect the audio source to xINN pin. AC-ground xINP pin by connecting a capacitor equal in value to the DCblocking capacitor on xINN pin. xINP input should be AC-grounded at the audio source, rather than at the device input, for achieving the best noise performance.

#### AC- or DC-Coupled Audio Signal

The preferred method to provide audio input is to AC-couple the audio source to xINP and xINN pins with capacitors.

It is also possible to DC-couple the audio source, provided the common-mode voltage of the audio source is close to 2.5V. If output impedance of audio source is high, or the common-mode voltage is far away from 2.5V, then risk of pop noise at turn-on is higher for a DC-coupled audio signal.

In addition, the further the common-mode voltage of the audio source is away from 2.5V, the more the audio source will have to source/sink DC current.

#### Input Capacitor Selection

For best THD performance, film capacitors are recommended at the Audio Inputs because they offer excellent stability over a wide temperature and voltage range. Use ceramic capacitors for cost-sensitive applications.

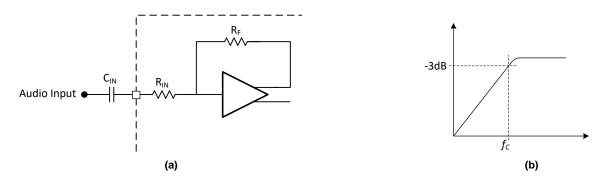

Input resistance of the PAM8965 can vary from  $15k\Omega$  at 26dB to  $105k\Omega$  at 6dB Gain setting. As a result, for AC-coupled applications, the cutoff frequency of high-pass filter that is formed at the input, varies with the Gain setting. The -3dB cutoff frequency is given by (1). Using the minimum value of R<sub>IN</sub>, which is  $15k\Omega$ , provides a minimum recommended value of C<sub>IN</sub> = 1µF to pass 20Hz to the amplifier.

$$f_{\rm C} = \frac{1}{2\pi R_{\rm IN} C_{\rm IN}} \tag{1}$$

Figure 2. (a) Audio Input Interface, (b) -3dB Cutoff Frequency of Audio Input High-Pass Filter

**PAM8965**

### Application Information (continued)

#### Audio Channel Gain

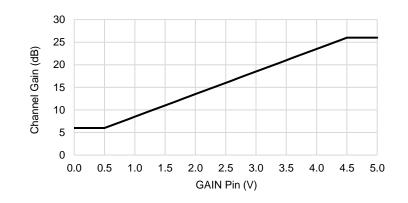

The PAM8965 audio channel gain is defined using the GAIN pin. The channel gain can be set between 26dB and 6dB at 0.5dB steps. Channel gain is accurate when it is based on internal resistors only. If using external resistor on the inputs to set the gain, then the device-to-device gain variation will be large. More importantly, even right and left channel gain will not match because the use of external resistors makes the channel gain dependent on the absolute values of these resistors.

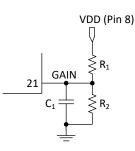

Connect a resistor divider between VDD and GND pins to define a voltage on the GAIN pin (Figure 3). This is important because GAIN is referenced to these supplies. Table 1 provides the resistor ratio required on the GAIN pin to obtain the required channel gain. Figure 4 show the relationship between the GAIN pin voltage and audio channel gain assuming  $V_{DD} = 5.0V$ . Aim for  $R_1 + R_2 \ge 100k\Omega$  to reduce current wasted in the divider. Place  $R_1$  and  $R_2$  close to the GAIN pin. A small 1nF capacitor can be placed near the pin to filter noise.

GAIN Resistor Ratio =

$$\frac{R_2}{R_1 + R_2}$$

(2)

Figure 3. GAIN Resistor Divider Setup

| Ratio       | Gain (dB) | Ratio | Gain (dB) | Ratio | Gain (dB) | Ratio | Gain (dB) | Ratio | Gain (dB) | Ratio       | Gain (dB) |

|-------------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------------|-----------|

| GND to 0.10 | 6.0       | 0.24  | 9.5       | 0.38  | 13.0      | 0.52  | 16.5      | 0.66  | 20.0      | 0.80        | 23.5      |

| 0.12        | 6.5       | 0.26  | 10.0      | 0.40  | 13.5      | 0.54  | 17.0      | 0.68  | 20.5      | 0.82        | 24.0      |

| 0.14        | 7.0       | 0.28  | 10.5      | 0.42  | 14.0      | 0.56  | 17.5      | 0.70  | 21.0      | 0.84        | 24.5      |

| 0.16        | 7.5       | 0.30  | 11.0      | 0.44  | 14.5      | 0.58  | 18.0      | 0.72  | 21.5      | 0.86        | 25.0      |

| 0.18        | 8.0       | 0.32  | 11.5      | 0.46  | 15.0      | 0.60  | 18.5      | 0.74  | 22.0      | 0.88        | 25.5      |

| 0.20        | 8.5       | 0.34  | 12.0      | 0.48  | 15.5      | 0.62  | 19.0      | 0.76  | 22.5      | 0.90        | 26.0      |

| 0.22        | 9.0       | 0.36  | 12.5      | 0.50  | 16.0      | 0.64  | 19.5      | 0.78  | 23.0      | 0.90 to 1.0 | 26.0      |

#### Table 1. GAIN Resistor Ratio vs. Audio Channel Gain (dB)

Figure 4. Channel Gain vs. GAIN Pin Voltage (with VDD = 5.0V)

#### Enable-Disable Control

EN pin on the PAM8965 is active-high. Voltage above V<sub>IH</sub> (1.5V) enables the device. EN pin is not limited to 5V operation and can be connected directly to VBAT, which has a maximum specification of 8.5V.

When EN pin is pulled below  $V_{IL}$  (0.5V), this disables the device and the audio outputs are muted and the boost converter is turned off. In the disabled or shutdown state, the device consumes only 0.7µA (typ). To achieve the best pop-noise performance, it is recommended to first disable the device before removing the power supply. Figure 5 shows one possible power-up and power-down sequence that would minimise output pop-noise.

After device turn-off, minimum wait of 400ms is required before asserting EN again.

EN pin has to be driven and cannot be left floating.

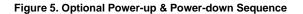

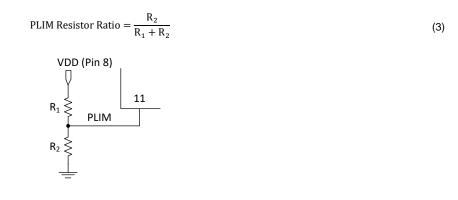

#### Non-Clip Power Limit (PLIM)

The PAM8965 features a non-clipping power limit that protects the speakers from burn out. PLIM pin should be set such that the maximum power rating of the speaker is matched with the maximum output power of the PAM8965.

#### Figure 6. PLIM Resistor Divider Setup

Connect a resistor divider between VDD and GND pins to define a voltage on PLIM pin as shown in Figure 6. This is important because the PLIM function is referenced to these supplies. Aim for  $R_1 + R_2 \le 20k\Omega$ . Place  $R_1$  and  $R_2$  close to the PLIM pin. Table 2 shows resistor ratio required on the PLIM pin to set the required output power.

Maximum PLIM voltage is 2.4V when using Power Limit function. PLIM = 2.4V will result in POUT = 9W for VBAT = 7.4V and RL =  $4\Omega$ . To disable the power limit function, connect PLIM to VDD (Pin 8).

|        |        | _     |           | $R_L = 4\Omega$ , $V_{BAT} = 7.4V$ | R <sub>L</sub> = 6Ω, V <sub>BAT</sub> = 3.7V |

|--------|--------|-------|-----------|------------------------------------|----------------------------------------------|

| R1 (Ω) | R2 (Ω) | Ratio | VPLIM (V) | Роит <b>(W)</b>                    | Роит <b>(W)</b>                              |

| 10K    | 3.0K   | 0.23  | 1.15      | 1.00                               | 1.20                                         |

| 10K    | 3.9K   | 0.28  | 1.40      | 2.00                               | 1.87                                         |

| 10K    | 4.7K   | 0.32  | 1.60      | 3.00                               | 2.40                                         |

| 10K    | 5.4K   | 0.35  | 1.75      | 4.00                               | 3.00                                         |

| 10K    | 6.2K   | 0.38  | 1.91      | 5.00                               | 3.67                                         |

| 10K    | 6.8K   | 0.40  | 2.02      | 6.00                               | 4.13                                         |

| 10K    | 7.5K   | 0.43  | 2.14      | 7.00                               | 4.73                                         |

| 10K    | 8.2K   | 0.45  | 2.25      | 8.00                               | 5.30                                         |

| 10K    | 9.1K   | 0.48  | 2.40      | 9.00                               | 6.00                                         |

|        | _      | _     | Vdd       | 11.50                              | 8.00                                         |

### Table 2. PLIM Pin Voltage (for V<sub>DD</sub> = 5.0V) or Resistor Ratio for Output Power (per Channel)

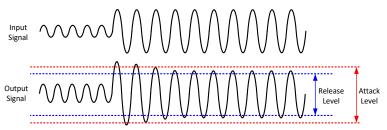

If instantaneous output power exceeds the defined PLIM value, then the amplifier triggers an attack cycle. Effectively, this begins a process of the PAM8965's amplifier gain stepping down with 0.5dB steps for every attack cycle. The gain is reduced with successive attack cycles until the output power drops to the value defined by the PLIM pin voltage as shown in Figure 7.

Figure 7. Output Power (per Channel) vs. PLIM Pin Voltage (for VDD = 5.0V)

Adjusting the amplifier's closed-loop gain to control the output power results in an extremely smooth control, which prevents harsh sounds due to saturation. This type of control avoids the output signal from being clipped, thus providing a much nicer listening experience. Figure 8 illustrates the non-clip power limit attack cycle.

Attack time for power limit is  $50\mu s$ , and release time is 340ms.

#### Figure 8. Non-Clip Power Limit Attack Cycle

#### Thermal Foldback

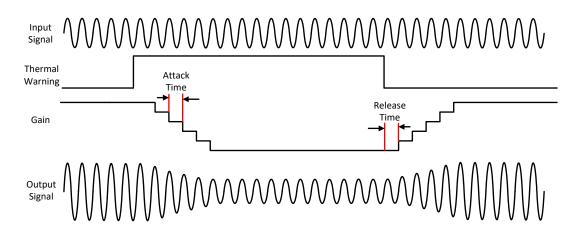

Device protection due to OTP results in abrupt turn-off and turn-on of sound. The primary purpose of thermal foldback (ThmFB) is to avoid interruption of sound due to OTP. The PAM8965's ThmFB feature works by stepping down the closed-loop gain of the amplifier once the die temperature reaches the ThmFB threshold. As the gain is stepped down, output power is reduced, which results in lower power dissipation thereby reducing the possibility of the device shutting down due to OTP.

Thermal Foldback threshold is set at +125°C. As with PLIM, this feature controls the closed-loop gain of the amplifier resulting in smooth transitions in the audio output. The full AGC range of 26dB to 6dB is available for ThmFB feature. Figure 9 shows an illustration of ThmFB attack and release cycles. The attack time is set at 170ms and the release time is 340ms.

#### Figure 9. Thermal Foldback Attack/Release Cycle

#### Fault Flag (FLT)

The PAM8965 features a fault flag, which is an open-drain output on the FLT pin. This pin supports full voltage range up to V<sub>BAT</sub>.

The following abnormal conditions are flagged on the FLT pin:

- UVLO on VBAT

- OVLO on VBAT

- Overtemperature shutdown (OTP)

- DC detected on any of the audio inputs (no autorecovery on this fault)

- Short-circuit protection (SCP) on any audio output

The open-drain FET turns on when fault occurs, and turns off once the fault is cleared. It is recommended to connect a  $100k\Omega$  pullup resistor from FLT pin to any voltage up to V<sub>BAT</sub>. If the aim is to minimize PCB component count, then FLT pin can be left floating.

#### Undervoltage Lockout (UVLO) on VBAT

When V<sub>BAT</sub> drops below the UVLO threshold of 2.45V (typ), the device enters a quasi-disabled state where the boost converter and the audio channels are turned off but a few blocks remain powered up. As a result, the current drawn from the battery in this state is higher than I<sub>SD</sub>. The device will auto-recover and repeat the startup sequence once V<sub>BAT</sub> goes above 2.8V.

#### Overvoltage Lockout (OVLO) on VBAT

When V<sub>BAT</sub> goes above the OVLO threshold of 8.9V (typ), the device enters a quasi-disabled state similar to UVLO condition. The device will autorecover and repeat the startup sequence once V<sub>BAT</sub> drops 350mV below the OVLO threshold.

#### **Overtemperature Protection**

To prevent device from overtemperature stress, the PAM8965 incorporates thermal shutdown, which turns the device off when junction temperature exceeds +150°C (typ). OTP has a hysteresis of +40°C. The system will resume operation after junction temperature goes below +110°C (typ). In OTP state, both the audio channels and the boost converter are turned off. This is not a latched fault.

For 1SxP applications, the high boost ratio results in very high boost switch currents. This reduces the efficiency of the system thereby increasing the junction temperature of the device. Depending on the physical enclosure the device is placed in, it may be necessary to use a heatsink if outputting maximum power with maximum boost ratio.

#### **DC Audio Detection**

The PAM8965 analyses the PWM output waveform to detect if a DC signal is being applied to the speakers. This can occur due to damaged capacitors at the audio inputs or due to shorts on the PCB. A DC signal can quickly over-heat and damage the speakers. By detecting DC in the output waveform rather than at the input, DC protection will kick-in at the same output level irrespective of the GAIN setting.

Once DC is detected on any of the outputs (P or N of right or left channel), both audio channels are turned off with all four audio outputs changing state to Hi-Z. The audio channels will remain off because this fault condition is latched. This ensures the speaker is protected against repeated exposure to DC voltage/current, which can cause damage.

Cycling EN or VBAT will clear the fault.

#### Short-Circuit Protection with Autorecovery for Audio Outputs

If the PAM8965 detects a short on any of the audio outputs, then it will change the state of all the audio outputs to Hi-Z. This protection not only saves the PAM8965 from damage but also prevents excessive currents from flowing from the supply, or to ground, which can cause damage to other components in the system. The PAM8965 protects against the following short conditions:

- Any audio output shorted to boosted supply (PVDD) or VBAT

- Any audio output shorted to Ground

- LOUTP shorted to LOUTN

- ROUTP shorted to ROUTN

Once any of the above-mentioned short is detected, then all the audio outputs are immediately disabled. The auto-recovery time is 340ms (typ). After this time has elapsed, the device will restart the outputs. If the short persists, the device will continue to trigger short protection after each autorecovery.

#### **Spread Spectrum Modulation**

The PAM8965 features spread spectrum modulation, which randomizes the oscillator frequency to improve EMI performance.

SSM on the PAM8965 is center-spread with ±11% modulation.

With SSM enabled, EMI specification can be met with inexpensive ferrite bead filters rather than bulky low-pass LC filters at the audio output. Given that the boost switching frequency (768kHz) is twice that of Class-D PWM frequency (384kHz), to avoid audible beats between the two systems, the SSM spread added to both systems is synchronized.

Connect SSM pin to a voltage above V<sub>IH</sub> (1.5V) to enable SSM, or below V<sub>IL</sub> (0.5V) to disable it. This pin is compliant to VDD.

#### **EMI Requirement**

The PAM8965 features spread-spectrum modulation, which can be turned on to reduce emissions. With SSM enabled, the PAM8965 can provide high-efficiency Class-D amplification while minimizing interference to the surrounding circuits.

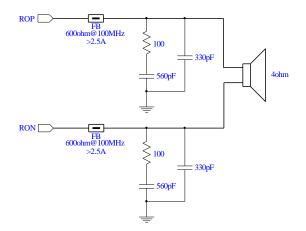

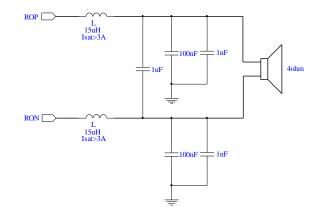

Two possibilities exist to meet FCC Class B regulations:

1. Ferrite Bead Filter

The PAM8965 EVM passes FCC Class B standard with a ferrite bead filter using 60cm long twisted-pair wires for 4Ω speakers and operating at 2x8W.

Only a low-cost ferrite bead filter is required for most applications. Select the ferrite bead type and size based on the application. A  $600\Omega@$ , 100MHz ferrite bead with a 330pF bypass capacitor and  $100\Omega+560$ pF snubber is recommended. A larger capacitor can be used to improve EMI filter, but system efficiency will be impacted. The filter should be placed close to the pins. Figure 10 shows an example of such a filter.

2. Low-Pass LC Filter

For long wires, it is recommended to use an LC filter to supress EMI. If the amplifier is close to sensitive circuits, then LC filter will provide better EMI filtering than ferrite filter. In addition, LC filter will have a smaller detrimental impact on system efficiency than a ferrite filter. Again, this filter should be placed close to the pins. See Figure 11 for details.

#### Figure 10. Typical Ferrite Bead Filter

Figure 11. Typical LC Filter for BTL, Cutoff Frequency = 28kHz, Speaker Impedance =  $4\Omega$

3. Snubber Circuit

A snubber circuit can be added to the booster switching inductor, See option "A" in Figure 14 for details.

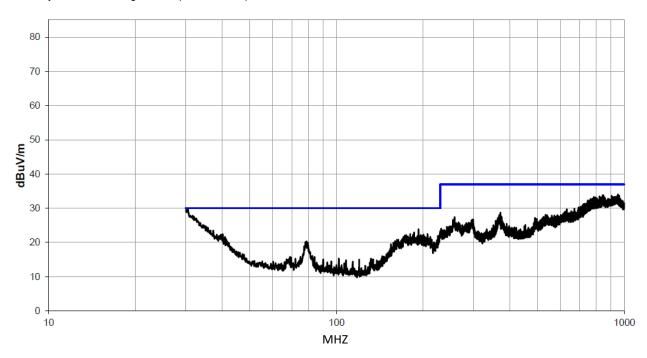

### **EMI Performance**

PAM8965 passes CISPR 32 Class B EMI test driving 2x8W into 4Ω left/right speakers with 60cm long twisted-pair wires using Diodes Incorporated's released PAM8965EVM (v1.1, 2 layer board) which has options EMI options "A", "B" and "C" installed (Please refer to Figure 14) on board. PCB layout is critical for good EMI performance, please refer to "PAM8965 EV Board User Guide" for details.

Figure 12. PAM8965 EMI Performance

#### Synchronous Boost Converter

The PAM8965 creates its own boosted power supply for the audio channels using a fully integrated synchronous boost converter. The converter delivers a fixed output voltage (VPVDD) of 9.2V from VBAT input supply that can range from 2.8V to 8.5V. It incorporates a 50m $\Omega$  power switch and a 50m $\Omega$  synchronous switch making it capable of delivering 2 × 12W in 4 $\Omega$  load with 2SxP battery, or 2 × 8W in 6 $\Omega$  load with 1SxP battery pack.

The current-mode boost converter operates in constant-frequency PWM mode for heavy loads and PFM (pulse-frequency modulation) mode when operating in light load condition. This allows the converter to operate at optimum efficiency throughout the load range. The boost control loop is internally compensated.

The converter features an out-of-audio mode, which ensures that the switching frequency on the SW node never falls in the audio band when the device is operating in PFM mode, typically restricting it to > 75kHz.

Cycle-by-cycle current limit monitors the current flowing in low-side FET, and turns it off immediately if the peak switch current reaches the threshold of 8A (typ). The converter also features an overvoltage protection on PVDD, which is set at 10.5V (typ).

#### 1SxP Battery – Special Considerations for $V_{BAT} \le 5.0V$

The efficiency of the system is lower when operating with 1SxP battery configuration as compared to 2SxP. The higher switch current due to higher boost ratio results in the device running hotter. The following three options may be implemented for 1SxP operation. Since this issue is related to heat dissipation, it is highly dependent on the PCB layout and metal thickness. Some applications may require all the options below, while some may only need one.

- 1. Use 4.7µH inductor

- High-current Schottky diode (e.g., SBR10U45SP5) placed between SW and PVDD (Pin 27 and 28): A Schottky diode, in parallel with boost high-side, should be placed very close to the pins. Bottom plane can be used for this connection. Omit this device if it cannot be placed within 10mm of the device pins.

Schottky diode (e.g., DFLS220L) and 10Ω resistor from VDD (Pin 8) to BST (Pin 26). This improves boost high-side drive at low V<sub>BAT</sub>, which results in improved system efficiency.

Figure 13. Boost Converter Waveforms, (a) PFM Mode, ILOAD = 0A, (b) PWM Mode, ILOAD = 1A

**Boost Inductor Selection**

It is critical to select a correct value of inductor for the boost converter because efficiency, transient behavior and loop stability rely on this selection. Three most important specifications of the inductor are its inductor value, DC resistance, and saturation current. In a boost regulator, the average DC current in the inductor is given by equation (4).

$$I_{L_{DC}} = \frac{PVDD * I_{OUT}}{V_{BAT} * \eta}$$

(4)

where,

$\begin{array}{ll} PVDD & \text{ is the output voltage of the boost regulator} \\ I_{OUT} & \text{ is the output current of the boost regulator} \\ V_{BAT} & \text{ is the supply voltage} \\ \eta & \text{ is the efficiency of the boost regulator} \end{array}$

For PVDD = 9.2V,  $I_{OUT}$  = 4.3A (assuming 600mV drop across the audio FETs, and 2 × 4 $\Omega$  load),  $V_{BAT}$  = 7.4V, and  $\eta$  = 90%, gives  $I_{L,DC}$  = 5.94A.

The Inductor peak-to-peak ripple current is given by the following equation:

$$\Delta I_{L,PP} = \frac{V_{BAT}(PVDD - V_{BAT})}{L \cdot f_{SW} \cdot PVDD}$$

(5)

where,

L is the inductor

$f_{SW}$  is the switching frequency of the Boost regulator

For  $f_{SW}$  = 768kHz and L = 4.7µH results in  $\Delta I_{L,PP}$  = 401mA (using the above mentioned values for V<sub>BAT</sub> and PVDD).

The peak inductor current,  $I_{L_PK}$ , can be calculated using (6).

$$I_{L_PK} = I_{L_DC} + \frac{\Delta I_{L_PP}}{2}$$

(6)

Plugging the above calculations in to (6), results in peak inductor current,  $I_{L PK} = 6.14A$ .

Note that boost converter's current limit is set at 8A. Even though peak inductor current calculated in this example is 6.14A, nevertheless, it is recommended to use an inductor with saturation current rating that is at least 25% higher than the current limit of 8A. There will be transients where the peak inductor current will reach the converter's current limit, especially at lower V<sub>BAT</sub> voltages. It is imperative that when this occurs, the inductor is not close to its saturation limit.

4.7µH inductor with saturation current rating of at least 10A is recommended.

#### **Capacitor Selection Guide**

Refer to Input Capacitor Selection for audio input capacitor calculation and recommendation.

Capacitor Value: $22\mu F$ Voltage Rating: $5 \times V_{BAT}$ Capacitor Type:X7R (ceramic)

V<sub>BAT</sub> is the power supply of the entire chip. It is important to place a bulk capacitor in parallel with a ceramic capacitor at this node, where the battery connects to the PCB. VBAT1 and VBAT2 are supply pins on the IC, and these should be Kelvin connected to the VBAT terminal on the PCB.

Where the bulk capacitor acts as a large storage, the ceramic capacitor provides a low impedance path for high-frequency noise due to its low equivalent series resistance (ESR).

Capacitors on the VBAT terminal and on the VBAT1 and VBAT2 pins can be scaled based on the VBAT supply used in the system. As a rule-of-thumb, use  $2 \times V_{BAT}$  voltage rating for electrolytics, and  $5 \times V_{BAT}$  voltage rating for ceramics.

VBAT1 is the primary power supply for the PAM8965. A number of internal startup and regulation circuitry is powered off VBAT1. Place these capacitors close to the pin.

$\begin{array}{ll} \mbox{VBAT2 (Pin 29)} \\ \mbox{Capacitor Value:} & 10 \mbox{$\mu$F$} \\ \mbox{Voltage Rating:} & 5 \times \mbox{$V_{BAT}$} \\ \mbox{Capacitor Type:} & X7R (ceramic) \end{array}$

VBAT2 supplies the boost internal circuitry, including regulators that help drive the power transistors. Thus, a larger capacitor of 10µF is recommended on VBAT2. Place this capacitor close to the pin.

VDD (Pin 8) Capacitor Value: 22µF in parallel with 0.1µF Voltage Rating: 25V Capacitor Type: X7R (ceramic)

The PAM8965's VDD Pin is the output of an internal 5V LDO regulator. Place these capacitors close to the VDD pin. This regulator's output should not be used to drive any external circuitry.

Bootstrap Capacitors (Pin 15, 17, 26, 34, 36)Capacitor Value:0.1µFVoltage Rating:25VCapacitor Type:X7R (ceramic)

All the bootstrap pins, including both audio channels (RBSTP, RBSTN, LBSTP, LBSTN) and the boost converter (BST), require a 0.1µF X7R capacitor on each pin. The capacitors must be connected from the bootstrap pins to their corresponding switching output. Place these capacitors close to the pins.

PVDD Boost Output (Pin 27 shorted with Pin 28)

| Capacitor Value:                    | 1000µF                                           |

|-------------------------------------|--------------------------------------------------|

| Voltage Rating:                     | 25V                                              |

| Capacitor Type:                     | Aluminium Polymer Electrolytic                   |

| Capacitor Value:<br>Voltage Rating: | $10\mu F$ 033 $\mu F,$ 2x330pF in parallelel 50V |

Capacitor Type: X7R (ceramic)

The PAM8965 is a high-performance audio amplifier that requires adequate audio power supply decoupling to ensure the total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents ringing oscillations caused by long leads between the amplifier and the speaker.

PVDD (Pin 27, 28), which is the boost converter's output, is the primary power supply for both the audio channel's H-bridges (Pin 16 and Pin 35). Boost converter output requires a bulk capacitor, and four ceramic capacitors to provide a clean supply to the audio channels. Place the ceramic capacitors close to the pins.

This regulator output should not be used to drive any external circuitry.

LPVDD & RPVDD (Pin 16 & Pin 35) Capacitor Value: 1µF and 0.1µF in parallel Voltage Rating: 50V Capacitor Type: X7R (ceramic)

LPVDD & RPVDD are supply pins for the audio H-bridge. For adequate noise filtering, each channel's supply shares a bulk aluminium polymer electrolytic capacitor of 1000µF with boost output, along with ceramic capacitors. Place the ceramic capacitor close to the pins.

### Additional Application Feasibilities

Other than typical applications with dynamic speaker load, the PAM8965 is also capable of wide varieties of applications to drive other types of loads, including high-capacitive ceramic speaker and Linear Resonant Actuator (LRA). For exploring these applications, please refer to related sales representative or Diodes Incorporated' Field Application team for further application support.

PAM8965

### Application Information (continued)

Figure 14. Typical Application Circuit for PAM8965 in BTL Mode

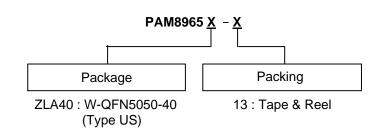

### **Ordering Information**

| Orderable Part Number | Package Code | Package                | Packing |                 |  |

|-----------------------|--------------|------------------------|---------|-----------------|--|

| Orderable Part Number | Fackage Code | Fackage                | Qty.    | Carrier         |  |

| PAM8965ZLA40-13       | ZLA40        | W-QFN5050-40 (Type US) | 3000    | 13" Tape & Reel |  |

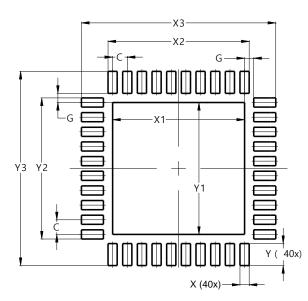

### **Marking Information**

W-QFN5050-40 (Type US)

DH = Manufacturer's Code Marking

PAM8965 = Marking ID

YY = Year (ex: 24 = 2024)

WW = Week (01 to 52, 52 Represents 52 and 53 weeks)

XX = Internal Code

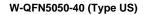

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

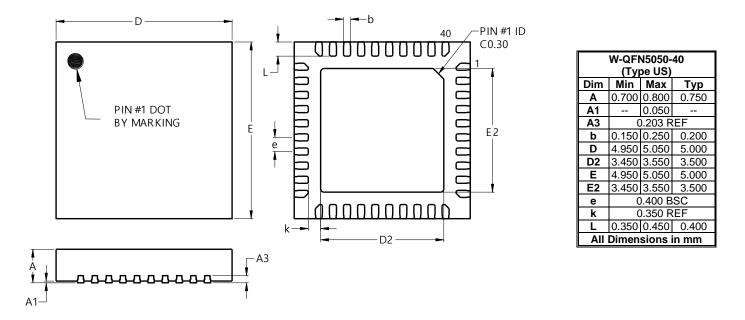

## **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

W-QFN5050-40 (Type US)

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.400            |

| G          | 0.250            |

| Х          | 0.250            |

| X1         | 3.600            |

| X2         | 3.850            |

| X3         | 5.300            |

| Y          | 0.600            |

| Y1         | 3.600            |

| Y2         | 3.850            |

| Y3         | 5.300            |

### **Mechanical Data**

- Moisture Sensitivity: Level 3 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per J-STD-002, Test B1 (3)

- Weight: 0.066 grams (Approximate)

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com