## eUSB to USB 2.0 / USB 2.0 to eUSB 1.2V Digital I<sup>2</sup>C I/O Repeater

## Description

The PI3EUSB1101 eUSB2 repeater is an interface between legacy USB 2.0 systems and lower voltage SoCs based on modern process geometries. The device is compliant with the Embedded USB 2.0 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification and supports eUSB2 operations and protocol.

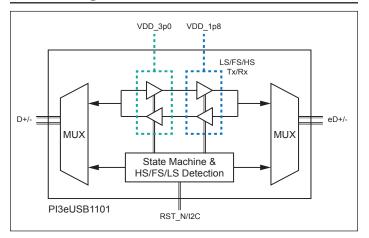

## **Block Diagram**

### **Features**

- Low Skew Outputs: <80ps •

- Compliant with the Latest USB 2.0 Specification

- Compliant with Embedded USB 2.0 (eUSB2) Physical Layer Specification Rev. 1.2

- Dual Role Capable ٠

- Integrated and Configurable Pull-Down Resistors on Both • eUSB2 and USB 2.0 Ends

- Integrated and Configurable Pull-Up Resistors on USB 2.0 Port

- Supports All USB 2.0 Speed Modes through Speed Detection and Negotiation

- High Speed Operation (480Mb/s)

- Full Speed Operation (12Mb/s)

- Low Speed Operation (1.5Mb/s)

- Auto Resume (remote wake-up)

- Asynchronous Wake-Up

- Provides Bus-Keeper Function for Device Wake-Up at Host Mode

- Supports 1.2V I<sup>2</sup>C I/O

- Supports x4 I<sup>2</sup>C ID Address

- ESD Performance

- BBM All Pins +/-8KV

- CDM All Pins +/-1KV

- Contact Discharge (IEC61000-4-2) for USB 2.0 D+/-+/-8KV

- Low Power Consumption

- Typical = 87mW Nominal Power during HS USB 2.0/eUSB2 Communication

- Analog Trimming

- Tx Amplitude Adjusts

- Tx EQ Adjusts

- Tx Drive Strength Adjusts

- Rx Sensitivity Tuning

- Charger Compliance •

- Ability to Keep D+/D- Lines in Hi-Z for APSD

- Chirp Levels

- Chirp J Differential Voltage (VCHIRPJ) is +700 to +1100 mV • Chirp K Differential Voltage (VCHIRPK) is -900 to -500 mV

- Squelch Detectors on Both eUSB2 and USB 2.0 Ports

- Configurable HS Disconnect Detector at USB 2.0 Port

- De-Glitch of ≥100ns on RST N

- Ambient Temperature: -40°C to 85°C

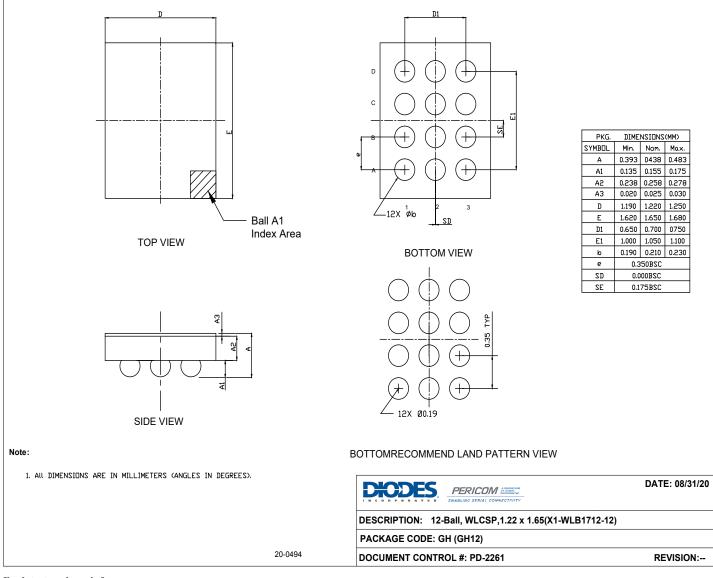

- Packaging (Pb-free & Green): <sup>12-ball</sup>, WLCSP (GH) 1.65mm x 1.22mm x 0.35mm pitch

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

- No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. 1.

- 2 See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds. 3.

Notes:

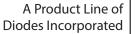

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Signal Type   | Description                                                                               |

|------------|----------|---------------|-------------------------------------------------------------------------------------------|

| D1         | DGND     | Ground        | Digital ground                                                                            |

| D2         | VDD_1P8  | Power         | 1.8V supply for analog circuitry                                                          |

| D3         | VDD_3P0  | Power         | 3.3V supply for analog circuitry                                                          |

| C1         | e_D+     | Analog        | eUSB2 Positive signals                                                                    |

| C2         | I2C_ADD  | Digital Input | I2C address setup. Refer to Table 2. VDD: 1.8V                                            |

| C3         | D+       | Analog        | USB 2.0 Positive signals                                                                  |

| B1         | e_D-     | Analog        | eUSB2 Negative signals                                                                    |

| B2         | RST_N    | Digital Input | Active low reset with internal 20k pulled to 1.8V. When tied to low, disable 20k resistor |

| B3         | D-       | Analog        | USB 2.0 Negative signals                                                                  |

| A1         | AGND     | Ground        | Analog ground                                                                             |

| A2         | SDA      | Digital I/O   | I2C data pin; TX/RX EQ initial setting                                                    |

| A3         | SCL      | Digital Input | I2C clock pin; TX/RX EQ initial setting                                                   |

# **Application Information**

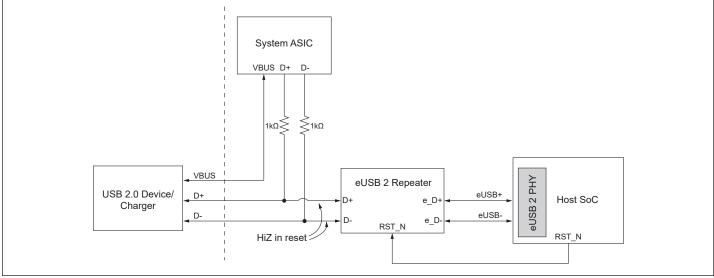

## **USB 2.0 Hi-Z During Reset**

The eUSB2 repeater will often be used in a system where the USB 2.0 D+/D- lines will be connected both externally (to a device, or charger, say) and internally to another ASIC in the system. In such cases there is often a period of time where the USB 2.0 device and system ASIC will communicate to each other over the D+/D- lines. Because of this, the D+/D- lines must always be held in a high impedance (Hi-Z) state until RST N is de-asserted, even while all supplies are actively enabled to the repeater.

Figure 1. System Connectivity Example of eUSB2 Repeater

## Auto Resume (Peripheral Initiated)

When a peripheral (such as a USB audio headset) is trying to resume active communication after the host has put the bus in suspend, it will assert a Resume K signal on the bus, which – depending on bus speed – will either be D+High and D-Low, or vice versa. However, the peripheral is only required to maintain the Resume K state for 1-15 ms, and if the device holds the state on the low end of this requirement (~1 ms), the Resume K state may not be held long enough by the peripheral for it to still be in the K state when the host responds, which may mean that the peripheral will not behave as intended once the host enters resume and it will instead go back to L2.

Therefore, bus keepers need to be employed in the repeater. These keepers will actively drive the state of the D+/D- lines even after the peripheral has stopped driving D+/D- in the Resume K state. The repeater needs to have the keepers active until the host resumes driving the bus so that host/peripheral communication can resume. The repeater will take the D+/D- lines out of Hi-Z when a control bit has been set via a PBUS register write. (Likewise, clearing this bit will force the D+/D- lines back to Hi-Z.)

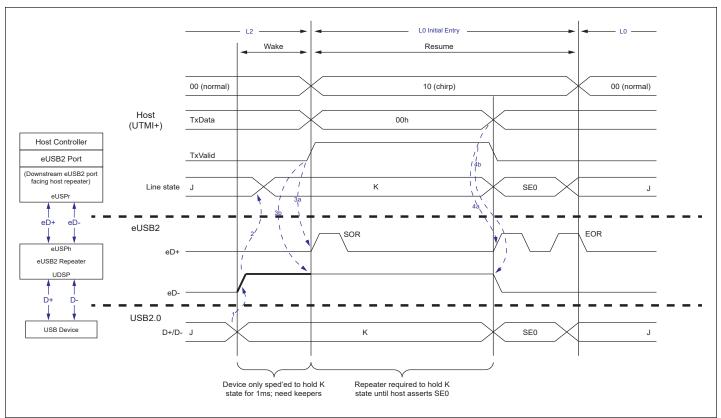

This is depicted in Figure 2. The sequence of events is as follows (numbers correspond to arrows in Figure 2):

1. While in L2, the device wants to wake up the host, so it asserts the K state using D+/D-.

2. When the eUSB2 repeater sees the K state, it drives eD-High (bold line depicts eUSB2 repeater driving line state).

3. When the host sees eD-go high, it changes to K state and begins Wake.

4. When the host leaves the Wake state, it drives eD+High for the start of resume pulse (3a), at which time the eUSB2 repeater will release control of eD- (3b).

5. When the host TxData has changed and is valid in the SE0 state, it drives eD-/eD+ appropriately, which causes the eUSB2 repeater to drive a SE0 on the D+/D- lines and put the USB device back into L0.

NOTE:

Unless the USB 2.0 device still sees the K state when the SE0 is driven from the repeater, it will not necessarily understand that a wakeup has occurred and can remain in suspend. Therefore, the eUSB2 repeater needs to implement bus keepers to keep the D+/D- lines driven in the K state until the host drives eD+High (happens after TxValid goes back Low at the End of Resume (EOR)).

Figure 2. Auto Resume Signaling (Peripheral Initiated) in Host Repeater Mode

### **Auto Resume (Host Initiated)**

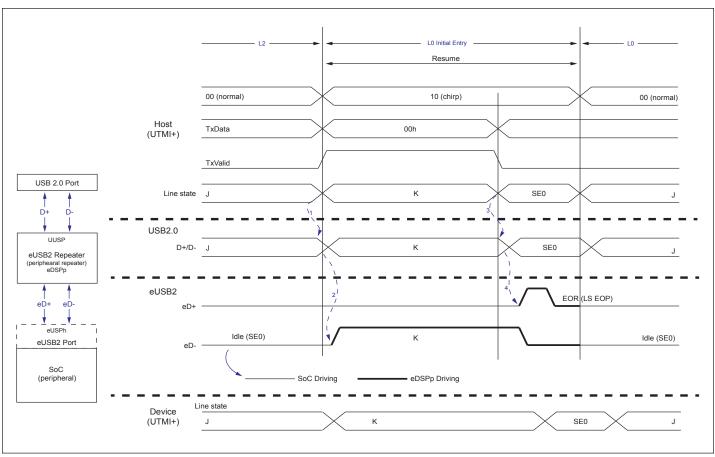

Another auto resume case is where the SoC is the peripheral and has the eUSB2 repeater attached, and the host initiates the resume. This is depicted in below in Figure 3.

In this case, the host internal line state will transition from J to K and the host will drive D+/D- to the K state (arrow 1 in Figure 3). When it sees the K state on D+/D-, the eUSB2 repeater will drive the K state on eD+/eD- by driving eD-HIGH. After a short time, the host will drive a SE0 on D+/D- (arrow 3) and the repeater will drive eD+HIGH, eD-LOW, then eD- back low to the SE0 state at the EOR (arrow 4).

Figure 3. Auto Resume Signaling (Host Initiated) in Peripheral Repeater Mode

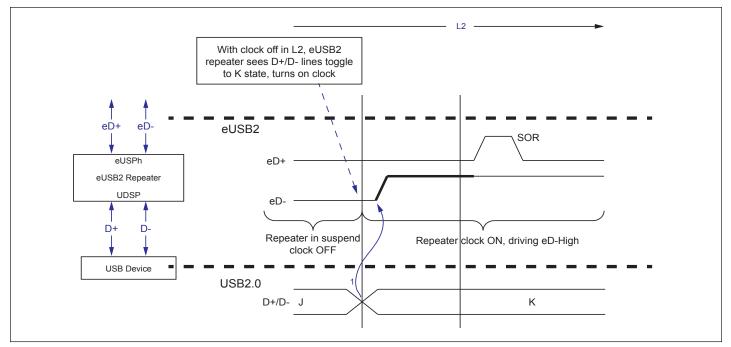

### Asynchronous Wake-Up

During L2 suspend the system clock will be turned off for optimum power savings. However, the eUSB2 repeater must be able to propagate the Resume K signaling from the peripheral to the SoC's eUSB2 PHY during L2 suspend. Therefore, the eUSB2 repeater must have a mechanism for the repeater to respond to the Resume K signal asynchronously, or without the clock active.

This is shown in Figure 4. The USB 2.0 device will attempt to come out of L2 suspend by toggling the D+/D- lines from 'J' to 'K' state. Even with the clock off, the eUSB2 repeater needs to recognize this change of line state, turn on the system clock, and follow the normal resume protocol (as described in more detail above) by driving eD-High so that the eUSB2 PHY in the SoC can respond.

#### Figure 4. Asynchronous Wake-up Waveforms

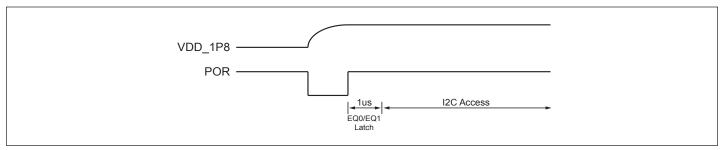

Figure 5. EQ0 and EQ1 Strapping Pin Latch Up Waveform

#### **Device Function Modes**

Repeater Mode

#### Table 1. Number of Hubs Supported with Host and/or Peripheral Repeater

| Number of eUSB2<br>Repeaters | Number of Hubs<br>Operating at HS | Number of Hubs<br>Operating at FS |                                                  |

|------------------------------|-----------------------------------|-----------------------------------|--------------------------------------------------|

| 1                            | 4                                 | 2                                 | Number of hubs operating at FS is reduced due to |

| 2                            | 3                                 | 1                                 | $T_{e_{to}_{U_{DJ1}}}$ and $T_{RJR1}$ .          |

| 0                            | 5                                 | 5                                 | non-eUSB2 system for reference                   |

Deep Standby Mode, RST\_N could be used as a power down pin when asserted low, that will put device in lowest power mode.

### **Register Map**

The eUSB2 repeater shall have I2C-accessable 8-bit registers for setting analog tuning bits, mode setting, as well as for setting various test modes. The precise detail for each of these register settings will be provided in future releases of this document.

I2C\_ADD pin is for I2C ID address setting, please direct connect to VDD (1.8V) or GND.

#### Table 2. I2C Address Selection Table

| I2C ID Address |       |              |             |  |  |

|----------------|-------|--------------|-------------|--|--|

| GND            | VDD   | 200K Pull-up | 56K Pull-up |  |  |

| 8'hDE          | 8'hDA | 8'hD6        | 8'hDC       |  |  |

#### Table 3. TX/RX EQ Initial Setting

| TX/RX EQ Initial Setting  |         |         |         |             |  |  |  |  |

|---------------------------|---------|---------|---------|-------------|--|--|--|--|

| SCL                       | 1       | 0       | 1       | 0           |  |  |  |  |

| SDA                       | 1       | 1       | 0       | 0           |  |  |  |  |

| Default RX EQ of eUSB/USB | 0dB/0dB | 0dB/2dB | 1dB/2dB | 2dB/1dB     |  |  |  |  |

| Default TX EQ of eUSB/USB | 0dB/0dB | 0dB/3dB | 1dB/3dB | 1.5dB/1.5dB |  |  |  |  |

Note: When SCL and SDA are connected to I2C interface, please pull-up.

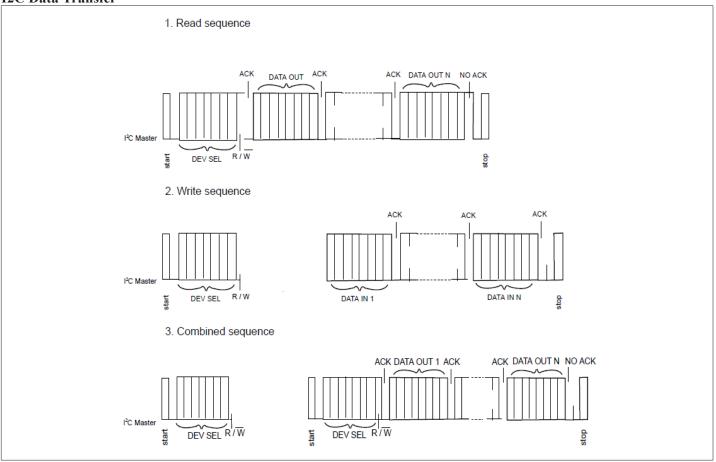

#### I2C Data Transfer

# SDA and SCL I/O for I<sup>2</sup>C-Bus

$V_{CC} = 1.62$  to 1.98V

| Symbol            | Parameter                                                               | Test Conditions | Min.                 | Max. | Units |

|-------------------|-------------------------------------------------------------------------|-----------------|----------------------|------|-------|

| V <sub>IH</sub>   | DC input logic high                                                     |                 | 0.77                 | 3.6  | V     |

| V <sub>IL</sub>   | DC input logic low                                                      |                 | -0.3                 | 0.39 | V     |

| V <sub>OL</sub>   | DC output logic low                                                     | $I_{OL} = 3mA$  |                      | 0.2  | V     |

| V <sub>hys</sub>  | Hysteresis of Schmott trigger input                                     |                 | 0.05*V <sub>CC</sub> |      | V     |

| t <sub>of</sub>   | Output fall time from $V_{IHmin}$ to $V_{ILmax}$ with bus cap. 10-400pF |                 |                      | 250  | ns    |

| f <sub>sCLK</sub> | SCLK clock frequency                                                    |                 |                      | 1000 | kHz   |

# **I2C Table**

| Byte | Byte 0: Mode Force Control 0 |      |                                                                                                              |         |  |  |

|------|------------------------------|------|--------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit  | Name                         | Туре | Control Function                                                                                             | Default |  |  |

| 7    | D+ line state                | R    | D+ line indicate 3V CMOS level<br>0b: normal operation<br>1b: pull high >3V. real time during LS/FS toggling | 0       |  |  |

| 6    | RESET                        | RW   | 0b: normal operation<br>1b: same behavior as RST_N pin                                                       | 0       |  |  |

| 5    | D+ bit 1.5K enable           | RW   | 0b: D+ 1.5k disable<br>1b: D+ 1.5k pull high                                                                 | 0       |  |  |

| 4    | Force D+ 1.5K engage         | RW   | 0b: normal operation<br>1b: determines bit5 D+ bit 1.5k engage                                               | 0       |  |  |

| 3    | SLEEP_FUN_BIT                | RW   | 0b: normal operation<br>1b: lowest power possible and cannot be waked by USB2/<br>eUSB2 ports                | 0       |  |  |

| 2    | USB_HI_Z                     | RW   | 0b: normal operation<br>1b: D+/D- HIZ                                                                        | 0       |  |  |

| 1    | Reserved                     | RW   | For internal usage                                                                                           | 0       |  |  |

| 0    | I2C_DISC_DET                 | RW   | 0b: normal operation<br>1b: enable TX EQ after 30 HS bit of uSOF's EOP                                       | 0       |  |  |

| Byte | Byte 1: USB2 TX EQ Control 1 |      |                                                                                                                                                                                                                |         |  |  |

|------|------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit  | Name                         | Туре | Control Function                                                                                                                                                                                               | Default |  |  |

| 7    |                              |      | Inside current bias for RX/TX-prebuffer LSFS buffer and HS detect buffer                                                                                                                                       |         |  |  |

| 6    | USB2_bias [1:0]<br>Reserved  | RW   | 00b: 50uA<br>01b: 45uA<br>10b: 55uA<br>11b: 60uA                                                                                                                                                               | 00b     |  |  |

| 5    | Reserved                     | RW   | For internal usage                                                                                                                                                                                             | 0       |  |  |

| 4    | Reserved                     | RW   | For internal usage                                                                                                                                                                                             | 0       |  |  |

| 3    | Reserved                     | RW   | For internal usage                                                                                                                                                                                             | 0       |  |  |

| 2    |                              |      | D+/D- TX HS EQ<br>000b: 0.0dB (no EQ)<br>001b: 0.5dB                                                                                                                                                           |         |  |  |

| 1    | USB2_TX_EQ [2:0]             | RW   | 010b: 1.0dB<br>011b: 1.5dB<br>100b: 2.0dB<br>101b: 3.0dB<br>110b: 4.5dB<br>111b: 6.0dB                                                                                                                         | 000Ъ    |  |  |

| 0    |                              |      | The settings of USB2_TX_EQ [2:0] (Byte 1), USB2_TX_<br>SWING [7:0] (Byte 6) and USB2_discon [2:0] registers may<br>affect each other. Please see details and follow the guidelines<br>in the application note. |         |  |  |

| Byte 2: eUSB2 TX EQ Output Current Control 2 |                      |      |                                                                                                                                                                                 |         |  |  |

|----------------------------------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit                                          | Name                 | Туре | Control Function                                                                                                                                                                | Default |  |  |

| 7                                            |                      |      | eUSB2 TX output amplitude<br>000b: 200mv                                                                                                                                        |         |  |  |

| 6                                            | eUSB2_TX_SWING [2:0] | RW   | 001b: -10mv (190mv)<br>010b: +10mv (210mv)<br>011b: +20mv (220mv)<br>100b: +30mv (230mv)                                                                                        | 000b    |  |  |

| 5                                            |                      |      | 101b: +40mv (240mv)<br>110b: +60mv (260mv)<br>111b: +80mv (280mv)                                                                                                               |         |  |  |

| 4                                            | RST_N PULL_HIGH      | RW   | 0b: enable 20K/2M pull up<br>1b: disalbe 20K/2M pull high                                                                                                                       | 0       |  |  |

| 3                                            | RST_N PULL_DOWN      | RW   | 0b: disable 100K pull down<br>1b: enalbe 100K pull down                                                                                                                         | 0       |  |  |

| 2                                            | BUS_KEPPER [0]       | RW   | Bus keeper [0]<br>Bus_keeper[1:0]<br>00b: Hold bus at both of eUSB and USB<br>01b: Hold bus only at eUSB<br>10b: No bus keeper function<br>11b: reserved and should not be used | 0       |  |  |

| 1                                            |                      |      | eD+/eD- TX HS EQ<br>00b: 0.0dB (no EQ)                                                                                                                                          |         |  |  |

| 0                                            | eUSB2_TX_EQ [1:0]    | RW   | 01b: 0.5dB<br>10b: 1.0dB<br>11b: 1.5dB                                                                                                                                          | 00Ъ     |  |  |

| Byte 3: USB2 RX EQ Control 3 |                 |      |                                                        |         |  |

|------------------------------|-----------------|------|--------------------------------------------------------|---------|--|

| Bit                          | Name            | Туре | Control Function                                       | Default |  |

| 7                            | USB2 Pup [1:0]  | RW   | USB2 LS/FS output pull high resistor<br>00b: 0% (36Ω)  | 00b     |  |

| 6                            | —USB2_Rup [1:0] | RW   | 01b: -20% (29Ω)<br>10b: -20% (29Ω)<br>11b: 0% (36Ω)    |         |  |

| 5                            | Reserved        | RW   | For internal usage                                     | 0       |  |

| 4                            | Reserved        | RW   | For internal usage                                     | 0       |  |

| 3                            |                 |      | USB2 RX EQ                                             |         |  |

| 2                            | USB2_RX_RQ      | DIAZ | 0x0: 0.0dB (no EQ)<br>0x1: 0.5dB                       | 00      |  |

| 1                            |                 | RW   | 0x2: 1.0dB<br>0x4: 2.0dB                               | 0x0     |  |

| 0                            |                 |      | 0x8: 3.0dB<br>others: reserved and should not be used. |         |  |

| Byte 4: eUSB2 RX EQ + Squelch Swing Selection Control 4 |                     |      |                                                                                                                                                                                 |         |  |

|---------------------------------------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit                                                     | Name                | Туре | Control Function                                                                                                                                                                | Default |  |

| 7                                                       |                     |      | eUSB2 squelch detection threshold<br>000b: 70mv                                                                                                                                 |         |  |

| 6                                                       | eUSB2_squelch [2:0] | RW   | 001b: -10mv (60mv)<br>010b: -20mv (50mv)<br>011b: -30mv (40mv)<br>100b: +10mv (80mv)                                                                                            | 0       |  |

| 5                                                       |                     |      | 101b: +20mv (90mv)<br>110b: +30mv (100mv)<br>111b: +30mv (100mv)                                                                                                                |         |  |

| 4                                                       | BUS_KEPPER [1]      | RW   | Bus keeper [1]<br>Bus_Keeper[1:0]<br>00b: Hold bus at both of eUSB and USB<br>01b: Hold bus only at eUSB<br>10b: No bus keeper function<br>11b: reserved and should not be used | 0       |  |

| 3                                                       |                     |      | eUSB2 RX EQ                                                                                                                                                                     |         |  |

| 2                                                       | eUSB2_RX_EQ [3:0]   | RW   | 0x0: 0.0dB (no EQ)<br>0x1: 0.5dB                                                                                                                                                | 0x0     |  |

| 1                                                       |                     |      | 0x2: 1.0dB<br>0x4: 2.0dB                                                                                                                                                        |         |  |

| 0                                                       |                     |      | 0x8: 3.0dB<br>others: reserved and should not be used.                                                                                                                          |         |  |

| Byte 5: USB2 Squelch Detection Offset Control 5 |                              |      |                                                                                                                                                   |         |  |

|-------------------------------------------------|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit                                             | Name                         | Туре | Control Function                                                                                                                                  | Default |  |

| 7                                               | REPEATER_REG [16]            | RW   | For digital EOP filter control<br>0b: disable filter<br>1b: enable filter                                                                         | 1       |  |

| 6                                               | CHIRP_KJ_TEST                | RW   | 1b: force into CHIRP test for High speed                                                                                                          | 0       |  |

| 5                                               |                              |      | USB2 RX squelch detection threshold                                                                                                               |         |  |

| 4<br>3<br>2<br>1                                | -<br>USB2_squelch [5:0]<br>- | RW   | 0x00: 110mv<br>0x01: -50mv (60mv)<br>0x02: -40mv (70mv)<br>0x04: -30mv (80mv)<br>0x08: -20mv (90mv)<br>0x10: -10mv (100mv)<br>0x20: +10mv (120mv) | 0x00    |  |

| 0                                               |                              |      | others: reserved and should not be used.                                                                                                          |         |  |

Byte 6: USB2 TX Output Swing Control 6 Bit Name **Control Function** Default Type USB2 TX output swing 7 0x00: 400mv 6 0x01: -50mv (350mv) 0x02: -25mv (375mv) 5 0x04: +25mv (425mv) 0x08: +50mv (450mv) 4 0x10: +75mv (475mv) RW 0x20: +100mv (500mv) 0x00 USB2\_TX\_SWING [7:0] 0x40: +125mv (525mv) 3 0x80: +175mv (575mv) others: reserved and should not be used. 2 The settings of USB2\_TX\_EQ [2:0] (Byte 1), USB2\_TX\_ 1 SWING [7:0] (Byte 6) and USB2\_discon [2:0] registers may affect each other. Please see details and follow the guidelines 0 in the application note.

| Byte ' | Byte 7: USB2 FS Output Res + Disconnection Detection Swing Setting Control 7 |      |                                                                                                                                                                                                                |         |  |  |

|--------|------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit    | Name                                                                         | Туре | Control Function                                                                                                                                                                                               | Default |  |  |

| 7      | Reserved                                                                     | RW   | For internal usage                                                                                                                                                                                             | 0       |  |  |

| 6      |                                                                              |      | USB2 disconnect threshold voltage<br>000b: 575mv<br>001b: -50mv (525mv)<br>010b: -25mv (550mv)                                                                                                                 |         |  |  |

| 5      | USB2_discon [2:0]                                                            | RW   | 010b: -25mv (550mv)<br>011b: +25mv (600mv)<br>100b: +50mv (625mv)<br>101b: +100mv (675mv)<br>110b: +175mv (750mv)<br>111b: +250mv (825mv)                                                                      | 000Ь    |  |  |

| 4      | -                                                                            |      | The settings of USB2_TX_EQ [2:0] (Byte 1), USB2_TX_<br>SWING [7:0] (Byte 6) and USB2_discon [2:0] registers may<br>affect each other. Please see details and follow the guidelines<br>in the application note. |         |  |  |

| 3      |                                                                              |      | USB2 LS/FS/HS output pull low resistor                                                                                                                                                                         |         |  |  |

| 2      | USB2_Rdn [3:0]                                                               |      | 0x0: 45Ω<br>0x1: -10%                                                                                                                                                                                          |         |  |  |

| 1      |                                                                              | RW   | 0x1: 10/0<br>0x2: -5%<br>0x4: +5%                                                                                                                                                                              | 0x0     |  |  |

| 0      |                                                                              |      | 0x8: +10%<br>others: reserved and should not be used.                                                                                                                                                          |         |  |  |

## Byte 8 - Byte 19: Reserved for Factory Control

| Byte 2 | 20: Revision ID, RO Bits       |      |                         |         |

|--------|--------------------------------|------|-------------------------|---------|

| Bit    | Name                           | Туре | Control Function        | Default |

| 7:0    | Revision ID                    | RO   | revision id             | 0x03    |

| Byte 2 | 21: Device ID, Low Byte, RO Bi | ts   |                         |         |

| Bit    | Name                           | Туре | <b>Control Function</b> | Default |

| 7:0    | Device ID [7:0]                | RO   | device id low word      | 0x00    |

| Byte 2 | 22: Device ID, High Byte, RO B | its  |                         |         |

|--------|--------------------------------|------|-------------------------|---------|

| Bit    | Name                           | Туре | <b>Control Function</b> | Default |

| 7:0    | Device ID [15:8]               | RO   | device id high word     | 0x11    |

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.) Note:

| Sto | age Temperature55°C to +150°C   |

|-----|---------------------------------|

|     | ction Temperature40°C to +125°C |

| Am  | bient Temperature40°C to +85°C  |

| Ana | log I/O (D+/-)0.5V to 5.5V      |

| Ana | log I/O (eD+/-)                 |

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Electrical Characteristics**

| Parameter           | Description              | Test Conditions                                                                   | Min. | Тур. | Max. | Units |

|---------------------|--------------------------|-----------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD_3P0</sub> | USB 2.0 analog voltage   |                                                                                   | 3.0  | 3.3  | 3.6  | V     |

| V <sub>DD_1P8</sub> | Analog supply voltage    |                                                                                   | 1.71 | 1.8  | 1.89 | V     |

| V <sub>IL</sub>     | Input voltage Low        | VDD18 = 1.8V, RST_N                                                               |      |      | 0.36 | V     |

| V <sub>IH</sub>     | Input voltage High       | VDD18 = 1.8V, RST_N                                                               | 0.84 |      |      | V     |

| I <sub>IL</sub>     | Low level input current  | VDD33 = 3.3V or 0V, VDD18 =<br>1.8V or 0V, V <sub>IL</sub> = 0V for SDA/<br>SCL   |      |      | 2    | uA    |

| I <sub>IH</sub>     | High level input current | VDD33 = 3.3V or 0V, VDD18 =<br>1.8V or 0V, V <sub>IH</sub> = 3.3V for SDA/<br>SCL |      |      | 2    | uA    |

| I <sub>IL</sub>     | Low level input current  | $\label{eq:VDD33} VDD33 = 3.3V, VDD18 = 1.8V, \\ V_{IL} = 0V \mbox{ for RST_N}$   |      |      | 2    | uA    |

| I <sub>IH</sub>     | High level input current | $\label{eq:VDD33} VDD33 = 3.3V, VDD18 = 1.8V, \\ V_{IH} = 1.8V \mbox{ for RST_N}$ |      |      | 2    | uA    |

| Pstby               | Deep standby mode        | Repeater powered, in reset.<br>I2C_ADD = GND or 1.8V                              |      | 80   |      | uW    |

| PDET                | Detach power             | Repeater powered, connected<br>to eUSB PHY and waiting to<br>attach               |      | 182  |      | uW    |

| PL2S                | L2 sleep power           | Link in L2, waiting for wake event                                                |      | 182  |      | uW    |

| PL1S                | L1 sleep power           | USB link in L1, waiting for L1 exit event                                         |      | 182  |      | uW    |

| PLSA                | LS active power          | Repeater in LS mode                                                               |      | 6.6  |      | mW    |

| PFSA                | FS active power          | Repeater in FS mode                                                               |      | 13.2 |      | mW    |

| PHSA                | HS active power          | Repeater in HS mode, maxi-<br>mum data rate, EQ 0dB, 450mV<br>swing               |      | 87   |      | mW    |

| Parameter           | Description                                                                | Test Conditions         | Min.                               | Тур. | Max.  | Units |

|---------------------|----------------------------------------------------------------------------|-------------------------|------------------------------------|------|-------|-------|

| USB 2.0 (D+/        | /D-)                                                                       |                         | I                                  |      | ·     |       |

| Input Levels        | for LS/FS                                                                  |                         |                                    |      |       |       |

| V <sub>IH</sub>     | Input High voltage (driven)                                                |                         | 2.0                                |      |       | V     |

| V <sub>IHZ</sub>    | Input High voltage (floating)                                              |                         | 2.7                                |      | 3.6   | V     |

| V <sub>IL</sub>     | Input Low voltage (driven)                                                 |                         |                                    |      | 0.8   | V     |

| V <sub>DI</sub>     | Differential input sensitivity                                             | (D+)-(D-)               | 0.2                                |      |       | V     |

| V <sub>CM</sub>     | Differential common mode range                                             | Includes VDI range      | 0.8                                |      | 2.5   | V     |

| Input Levels        | for HS                                                                     | 1                       | I                                  | I    |       |       |

| V <sub>HSSQ</sub>   | HS squelch detection threshold<br>(differential signal amplitude)          |                         | 100                                |      | 150   | mV    |

| V <sub>HSDSC</sub>  | HS disconnect detection<br>threshold (differential signal<br>amplitude)    |                         |                                    | 575  |       | mV    |

| V <sub>HSDIFF</sub> | HS differential input signal levels                                        |                         | Specified by eye pattern templates |      |       |       |

| V <sub>HSCM</sub>   | HS data signaling common<br>mode voltage range (guideline<br>for receiver) |                         | -50                                |      | 500   | mV    |

| T <sub>j_add</sub>  | Differential additive jitter                                               | Signal generator source |                                    |      | 50    | ps    |

| Output Level        | s for LS/FS                                                                |                         | ·                                  |      |       |       |

| V <sub>OL</sub>     | Output low voltage                                                         |                         | 0                                  |      | 0.3   | V     |

| V <sub>OH</sub>     | Output high voltage (driven)                                               |                         | 2.8                                |      | 3.6   | V     |

| V <sub>OSE1</sub>   | SE1 voltage                                                                |                         | 0.8                                |      |       | V     |

| V <sub>CRS</sub>    | Output signal crossover voltage                                            |                         | 1.3                                |      | 2.0   | V     |

| Output Level        | s for HS                                                                   |                         |                                    |      |       |       |

| V <sub>HSOI</sub>   | HS idle level                                                              |                         | -10                                |      | 10    | mV    |

| V <sub>HSOH</sub>   | HS data signal high                                                        |                         | 360                                | 400  | 440   | mV    |

| V <sub>HSOL</sub>   | HS data signal low                                                         |                         | -10                                |      | 10    | mV    |

| V <sub>CHIRPJ</sub> | Chirp J level (differential)                                               |                         | 700                                |      | 1100  | mV    |

| V <sub>CHIRPK</sub> | Chirp K level (differential)                                               |                         | -900                               |      | -500  | mV    |

| LS/FS Param         | ieters                                                                     |                         | ·                                  |      |       |       |

| R <sub>PU</sub>     | Bus pull-up resistor on up-<br>stream facing port                          |                         | 1.425                              | 1.5  | 1.575 | kΩ    |

| R <sub>PD</sub>     | Bus pull-down resistor on downstream facing port                           |                         | 14.25                              | 15   | 15.75 | kΩ    |

| Z <sub>INP</sub>    | Input impedance exclusive of pull-up/pull-down                             |                         | 300                                |      |       | kΩ    |

| Parameter                        | Description                                                                          | Test Conditions | Min.     | Тур. | Max.     | Units               |

|----------------------------------|--------------------------------------------------------------------------------------|-----------------|----------|------|----------|---------------------|

| V <sub>TERM</sub>                | Termination voltage for up-<br>stream facing port R <sub>PU</sub>                    |                 | 3.0      |      | 3.6      | V                   |

| HS Paramete                      | ers                                                                                  |                 |          |      |          |                     |

| V <sub>HSTERM</sub>              | Termination voltage in HS                                                            |                 | -10      |      | 10       | mV                  |

| T <sub>HSR</sub>                 | Rise time for HS (10%-90%)                                                           |                 | 100      |      |          | ps                  |

| T <sub>HSF</sub>                 | Fall time for HS (10%-90%)                                                           |                 | 100      |      |          | ps                  |

| Z <sub>HSDRV</sub>               | Driver output resistance (also<br>serves as FS termination which<br>with HS capable) |                 | 40.5     | 45   | 49.5     | Ω                   |

| eUSB2 (eD+/                      | eD-)                                                                                 |                 | i        |      |          |                     |

| LS/FS Param                      | eters (VCC = 1.1-1.2V)                                                               |                 |          |      |          |                     |

| V <sub>IL</sub>                  | Input low voltage                                                                    |                 | -0.1     |      | 0.35*VCC | V                   |

| V <sub>IH</sub>                  | Input high voltage                                                                   |                 | 0.65*VCC |      | 1.05*VCC | V                   |

| V <sub>HYS</sub>                 | Receive single-end hysteresis voltage                                                |                 | 0.04*VCC |      |          | V                   |

| V <sub>OL</sub>                  | Output low voltage                                                                   |                 |          |      | 0.15*VCC | V                   |

| V <sub>OH</sub>                  | Output high voltage                                                                  |                 | 0.85*VCC |      | VCC      | V                   |

| R <sub>SRC_LSFS</sub>            | Transmit output impedance                                                            |                 | 28       |      | 60       | Ω                   |

| HS Paramete                      | ers                                                                                  |                 |          |      |          |                     |

| V <sub>TX_DIF_</sub><br>term     | Transmit differential voltage<br>(terminated)                                        |                 | 165      | 200  | 245      | mV                  |

| V <sub>TX_CM</sub>               | Transmit common mode                                                                 |                 | 170      | 200  | 230      | mV                  |

| R <sub>SRC_HS</sub>              | Transmit source termination impedance                                                |                 | 32       | 40   | 48       | Ω                   |

| $\Delta R_{SRC_{HS}}$            | Source impedance mismatch                                                            |                 |          |      | 4        | Ω                   |

| V <sub>TX_CM_AC</sub>            | Transmit CM AC (50MHz-<br>480MHz)                                                    |                 |          |      | 30       | +/-mV <sub>PK</sub> |

| T <sub>RISE_FALL_</sub><br>TRM   | Transit rise and fall time (20%-<br>80%)                                             |                 | 100      |      |          | PS                  |

| ΔT <sub>RISE</sub> _<br>fall_trm | Transit rise/fall mismatch                                                           |                 |          |      | 25       | %                   |

| V <sub>RX_CM</sub>               | Receive common mode range                                                            |                 | 120      | 200  | 280      | mV                  |

| C <sub>RX_CM</sub>               | Receive center-tapped capaci-<br>tance                                               |                 | 15       |      | 50       | pF                  |

| V <sub>RX_DIF_</sub><br>sens     | Receive sensitivity (peak dif-<br>ferential)                                         |                 | 60       |      |          | +/-mV               |

| R <sub>RCV_DIF</sub>             | Differential receiver termina-<br>tion (repeater)                                    |                 | 72       | 80   | 88       | Ω                   |

| Parameter                     | Description                                               | Test Conditions         | Min. | Тур. | Max. | Units               |

|-------------------------------|-----------------------------------------------------------|-------------------------|------|------|------|---------------------|

| V <sub>SQUELCH</sub> _<br>DIF | Squelch detect threshold volt-<br>age (peak differential) |                         | 60   |      | 110  | mV                  |

| V <sub>CM_RX_AC</sub>         | Receiver AC common mode<br>(50MHz-480MHz)                 |                         |      |      | 60   | +/-mV <sub>PK</sub> |

| T <sub>j_add</sub>            | Differential additive jitter                              | Signal generator source |      |      | 50   | ps                  |

## **Switching Characteristics**

| Parameter          | Description                     | Test Conditions       | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------|-----------------------|------|------|------|-------|

| D+/D- FS Dri       | ver Switching Characteristics   |                       |      |      |      |       |

| T <sub>FR</sub>    | Rise Time (10%-90%)             | USB 2.0 specification | 4    |      | 20   | ns    |

| T <sub>FF</sub>    | Fall Time (10%-90%)             | USB 2.0 specification | 4    |      | 20   | ns    |

| D+/D- LS Dri       | ver Switching Characteristics   |                       |      |      |      |       |

| T <sub>LR</sub>    | Rise Time (10%-90%)             | USB 2.0 specification | 75   |      | 300  | ns    |

| T <sub>LF</sub>    | Fall Time (10%-90%)             | USB 2.0 specification | 75   |      | 300  | ns    |

| eD+/eD- LS/F       | S Driver Switching Characterist | ics                   |      |      |      |       |

| $T_{FR}/T_{FF}$    | Rise/Fall time (10%-90%)        | eUSB2 specification   | 2    |      | 6    | ns    |

| T <sub>RF_MM</sub> | Transmit rise/fall mismatch     | eUSB2 specification   |      |      | 25   | %     |

# **Timing Requirements**

| Parameter        | Description                                                                                                                                          |    | Тур. | Max. | Units |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------|-------|

| RESET Timin      | g                                                                                                                                                    |    |      |      |       |

| T_VDD18_<br>RAMP | Ramp time for VDD18 to reach min. 1.62V                                                                                                              |    |      | 2    | ms    |

| T_VDD33_<br>RAMP | Ramp time for VDD33 to reach min. 2.7V                                                                                                               |    |      | 2    | ms    |

| T_artn_b         | Duration for RST_N to be asserted low to complete reset while powered                                                                                | 10 |      |      | us    |

| T_ready          | Time for eUSB2 interface to be ready after RST_N is de-asserted<br>or both power suppliers reach minimum recommended voltages,<br>whichever is later |    |      | 3    | ms    |

# **Part Marking**

| yJ: Top Mark (PI3EUSB1101GHE)             |

|-------------------------------------------|

| *: Die Rev                                |

| YW: Date Code (Year&Workweek)             |

| ● Pin 1 location                          |

| Note: If Die Rev is "0", then there is no |

| Die Rev character.                        |

|                                           |

# **Packaging Mechanical**

12-WLCSP (GH)

#### For latest package info.

$please \ check: \ http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/pericom-packaging/packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-pericom-packaging-p$

## **Ordering Information**

| Orderable Part Number | Package Code | Package Description                          |

|-----------------------|--------------|----------------------------------------------|

| PI3EUSB1101GHEX       | GH           | 12-ball, 1.22 x 1.65mm (WLCSP) X1-WLB1712-12 |

#### Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm

- antimony compounds.

- 4. E = Pb-free and Green

5. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH RE-1 GARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MER-CHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described 2. herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3 Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5 Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/termsand-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6 Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7 While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8 Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/ important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com