A Product Line of Diodes Incorporated

PI4GTL2002

#### 2-Bit Bidirectional Low Voltage Translator

#### **Features**

Description

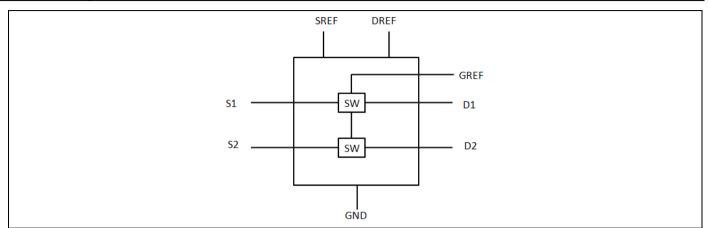

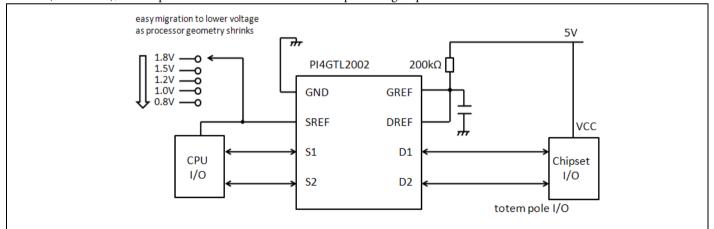

The Gunning Transceiver Logic - Transceiver Voltage Clamps (GTL-TVC) provide high-speed voltage translation with low ON-state resistance and minimal propagation delay.

The DIODES PI4GTL2002 provides 2 NMOS pass transistors (Sn and Dn) with a common gate (GREF) and a reference transistor (SREF and DREF). The device allows bidirectional voltage translations between 0.8V and 5.0V without use of a direction pin.

When the Sn or Dn port is LOW the clamp is in the ON-state and a low resistance connection exists between the Sn and Dn ports. Assuming the higher voltage is on the Dn port, when the Dn port is HIGH, the voltage on the Sn port is limited to the voltage set by the reference transistor (SREF). When the Sn port is HIGH, the Dn port is pulled to VCC by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user, without the need for directional control.

All transistors have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the transistors is symmetrical. Because all transistors in the device are identical, SREF and DREF can be located on any of the other two matched Sn/Dn transistors, allowing for easier board layout. The translator's transistors provide excellent ESD protection to lower voltage devices and at the same time protect less ESD-resistant devices.

# • 2-bit bidirectional translator

- Less than 1.5ns maximum propagation delay to accommodate Standard mode and Fast mode I2C-bus devices and multiple masters

- Allows voltage level translation between 0.8V, 1.2V, 1.5V, 1.8V, 2.5V, 3.3V and 5V buses, which allows direct interface with GTL, GTL+, LVTTL/TTL and 5V CMOS levels

- Provides bidirectional voltage translation with no direction pin

- Low 3.5Ω ON-state connection between input and output ports provides less signal distortion

- Supports hot insertion

- 5 V tolerant inputs

- Flow-through pinout for ease of printed-circuit board trace routing

- ESD protection exceeds 4KV HBM per JESD22-A114

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

- Packaging (Pb-free & Green):

- □ 8-Pin, MSOP (M)

- □ 8-Pin, VSSOP (V)

- □ 8-Pin, X2-DFN (HK)

- □ 8-Pin, SOT28 (TA)

- 8-Pin, SSOP (SS)

Notes:

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

**PI4GTL2002**

# **Block Diagram**

### Figure 1. Block Diagram

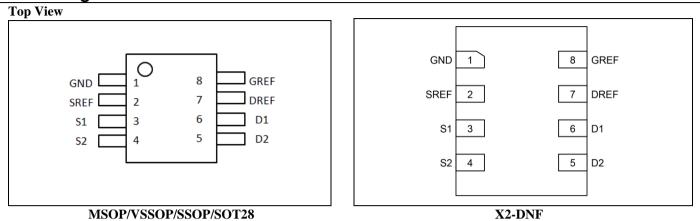

# Pin Configuration

# **Pin Description**

| Pin# | Pin Name | Description                                                                 |

|------|----------|-----------------------------------------------------------------------------|

| 1    | GND      | ground (0 V)                                                                |

| 2    | SREF     | low-voltage side reference supply voltage for S1 and S2                     |

| 3    | S1       | serial clock, low-voltage side; connect to SREF through a pull-up resistor  |

| 4    | S2       | serial data, low-voltage side; connect to SREF through a pull-up resistor   |

| 5    | D2       | serial data, high-voltage side; connect to DREF through a pull-up resistor  |

| 6    | D1       | serial clock, high-voltage side; connect to DREF through a pull-up resistor |

| 7    | DREF     | high-voltage side reference supply voltage for D1 and D2                    |

| 8    | GREF     | switch enable input; connect to DREF and pull-up through a high resistor    |

## **Function Description**

Function Selection, HIGH to LOW translation

Assuming Dn is at the higher voltage level.

H = HIGH voltage level; L = LOW voltage level; X = Don't care.

| GREF | DREF | SREF   | Input Dn | Output Sn | Transistor |

|------|------|--------|----------|-----------|------------|

| Н    | Н    | 0V     | Х        | Х         | off        |

| Н    | Н    | VTT    | Н        | VTT       | on         |

| Н    | Н    | VTT    | L        | L         | on         |

| L    | L    | 0V-VTT | Х        | Х         | off        |

- 1. GREF should be at least 1.5V higher than SREF for best translator operation.

- 2. Sn is not pulled up or pulled down.

- 3. Sn follows the Dn input LOW.

- 4. VTT is equal to the SREF voltage.

### Function Selection, LOW to HIGH translation

Assuming Dn is at the higher voltage level.

H = HIGH voltage level; L = LOW voltage level; X = Don't care.

| GREF | DREF | SREF   | Input Sn | Output Dn | Transistor |

|------|------|--------|----------|-----------|------------|

| Н    | Н    | 0V     | Х        | Х         | off        |

| Н    | Н    | VTT    | VTT      | Н         | nearly off |

| Н    | Н    | VTT    | L        | L         | on         |

| L    | L    | 0V-VTT | Х        | Х         | off        |

1. GREF should be at least 1.5V higher than SREF for best translator operation.

2. Sn is not pulled up or pulled down.

3. Sn follows the Dn input LOW.

4. VTT is equal to the SREF voltage.

### **Maximum Ratings**

| Storage Temperature              | $-65^{\circ}$ C to $+150^{\circ}$ C |

|----------------------------------|-------------------------------------|

| Reference Voltage <sup>(2)</sup> |                                     |

| Reference Bias Voltage           |                                     |

| DC Input Voltage                 | -0.5V to +6.0V                      |

| Control Input Voltage (EN)       | -0.5V to+6.0V                       |

| Channel Current (DC)             |                                     |

| Input Clamping Current           | 50mA                                |

| ESD: HBM Mode                    |                                     |

|                                  |                                     |

Note:

1. Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. The input and input/output negative voltage ratings may be exceeded if the input and input/output clamp current ratings are observed.

# **Recommended Operation Conditions**

| VCC = 2.7V to 5.5V; GND = 0V; $T_A = -40^{\circ}C$ to +85°C; unless otherwise specified |                                       |                 |      |      |      |      |  |

|-----------------------------------------------------------------------------------------|---------------------------------------|-----------------|------|------|------|------|--|

| Symbol                                                                                  | Parameter                             | Test Conditions | Min. | Тур. | Max. | Unit |  |

| V <sub>I/O</sub>                                                                        | Voltage on an input/output pin        | S1, D1, S2, D2  | 0    | -    | 5    | V    |  |

| SREF                                                                                    | Reference voltage <sup>(1)</sup>      | SREF            | 0    | -    | 5    | V    |  |

| DREF                                                                                    | Reference bias voltage <sup>(2)</sup> | DREF            | 0    | -    | 5    | V    |  |

| V <sub>GREF</sub>                                                                       | Input voltage on pin GREF             | -               | 0    | -    | 5    | V    |  |

| I <sub>(pass)</sub>                                                                     | Pass switch current                   | -               | -    | -    | 64   | mA   |  |

| T <sub>A</sub>                                                                          | Ambient temperature                   | -               | -40  | -    | 85   | °C   |  |

# **DC Electrical Characteristics**

| Parameter           | Description                                    | Test Condition                           | ns <sup>(1)</sup>         | Min | <b>Typ.</b> <sup>(2)</sup> | Max  | Unit |

|---------------------|------------------------------------------------|------------------------------------------|---------------------------|-----|----------------------------|------|------|

| Input and o         | utput DB and SB                                | •                                        |                           |     |                            |      |      |

| V <sub>IK</sub>     | Input clamping voltage                         | $I_I = -18 mA; V_{GREF} = 0V$            |                           | -   | -                          | -1.2 | V    |

| I <sub>IH</sub>     | HIGH-level input current                       | $V_I = 5V; V_{GREF} = 0V$                |                           | -   | -                          | 5    | μΑ   |

| C <sub>GREF</sub>   | Input capacitance on pin GREF                  | $V_I = 3V \text{ or } 0V$                |                           | -   | 11                         | -    | pF   |

| Cio(off)            | off-state input/output capacitance<br>(Sn, Dn) | $V_{O} = 3V$ or $0V$ ; $V_{GREF} = 0V$   |                           | -   | 4                          | -    | pF   |

| C <sub>io(on)</sub> | on-state input/output capacitance<br>(Sn, Dn)  | $V_0 = 3V \text{ or } 0V; V_{GREF} = 3V$ |                           | -   | 10.5                       | -    | pF   |

|                     |                                                |                                          | $V_{GREF} = 4.5V$         | -   | 3.5                        | 5.5  | Ω    |

|                     |                                                | $V_{I} = 0V;$<br>$I_{O} = 64mA$          | $V_{\text{GREF}} = 3V$    | -   | 4.7                        | 7.0  | Ω    |

|                     |                                                | $I_0 = 64mA$                             | $V_{\text{GREF}} = 2.3 V$ | -   | 6.3                        | 9.5  | Ω    |

| Ron                 | ON-state resistance <sup>(2)</sup>             |                                          | $V_{GREF} = 1.5V$         | -   | 60                         | 140  | Ω    |

| KUII                | (Sn, Dn)                                       | $V_{I} = 2.4V;$                          | $V_{GREF} = 4.5V$         | 1   | 6                          | 15   | Ω    |

|                     |                                                | $I_{O} = 15mA$                           | $V_{GREF} = 3V$           | 20  | 60                         | 140  | Ω    |

|                     |                                                | $V_{I} = 1.7V;$ $I_{O} = 15mA$           | $V_{GREF} = 2.3V$         | 20  | 60                         | 140  | Ω    |

Notes: 1) All typical values are at  $T_A = 25$  °C.

Measured by the voltage drop between the S1 and S2, or D1 and D2 terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

# **Dynamic Characteristics**

|                  | to +85°C; unless otherv                |                                     |      | $C_L = 50 pF$ |      | $C_L = 30 pF$ |     | $C_L = 15 pF$ |      |

|------------------|----------------------------------------|-------------------------------------|------|---------------|------|---------------|-----|---------------|------|

| Symbol           | Parameter                              | Conditions                          | Min  | Max           | Min  | Max           | Min | Max           | Unit |

| $V_{GREF} = 3$   | $.3V; V_{\rm H} = 3.3V; V_{\rm L} = 0$ | $V; V_{M} = 1.15V$                  |      |               |      |               |     |               |      |

| t <sub>PLH</sub> | LOW-to-HIGH                            | from (input) S2 or D2               | 0    | 0.8           | 0    | 0.6           | 0   | 0.3           | ns   |

| <b>U</b> PLH     | propagation delay                      | to (output) S1 or D1                | 0    | 0.8           | 0    | 0.0           | 0   | 0.5           | 115  |

| t <sub>PHL</sub> | HIGH-to-LOW                            | from (input) S2 or D2               | 0    | 1.2           | 0    | 1             | 0   | 0.5           | ns   |

| <b>U</b> PHL     | propagation delay                      | to (output) S1 or D1                | 0    | 1.2           | 0    | 1             | 0   | 0.5           | 115  |

| $V_{GREF} = 2$   | $.5V; V_{\rm H} = 2.5V; V_{\rm L} = 0$ | $V; V_{M} = 0.75V$                  |      |               |      |               |     |               |      |

| t <sub>PLH</sub> | LOW-to-HIGH                            | from (input) S2 or D2               | 0    | 1             | 0    | 0.7           | 0   | 0.4           | ns   |

| <b>U</b> PLH     | propagation delay                      | to (output) S1 or D1                | 0    |               | 0    |               |     |               | 113  |

| t <sub>PHL</sub> | HIGH-to-LOW                            | from (input) S2 or D2               | 0    | 1.3           | 0    | ) 1           | 0   | 0.6           | ns   |

| <b>U</b> PHL     | propagation delay                      | to (output) S1 or D1                | 0    |               | 0    |               |     |               | 115  |

| $V_{GREF} = 3$   | $.3V; V_{\rm H} = 2.3V; V_{\rm L} = 0$ | $V; V_T = 3.3V; V_M = 1.15V; R_L =$ | 300Ω |               |      |               |     |               |      |

| t <sub>PLH</sub> | LOW-to-HIGH                            | from (input) S1 orD1                | 0    | 0.9           | 0    | 0.6           | 0   | 0.4           | ns   |

| <b>U</b> PLH     | propagation delay                      | to (output) S2 or D2                | 0    | 0.9           | 0    |               |     | 0.4           | 115  |

| t <sub>PHL</sub> | HIGH-to-LOW                            | from (input) S1 or D1               | 0    | 1.4           | 0    | 1.1           | 0   | 0.7           | ne   |

| <b>U</b> PHL     | propagation delay                      | to (output) S2 or D2                | 0    | 1.7           | .4 0 | 1.1           | 0   | 0.7           | ns   |

| $V_{GREF} = 2$   | $.5V; V_{\rm H} = 1.5V; V_{\rm L} = 0$ | $V; V_T = 2.5V; V_M = 0.75V; R_L =$ | 300Ω |               |      |               |     |               |      |

| t                | LOW-to-HIGH                            | from (input) S1 orD1                | 0    | 1             | 0    | 0.6           | 0   | 0.4           | no   |

| t <sub>PLH</sub> | propagation delay                      | to (output) S2 or D2                | 0    | 1             | U    | 0.6           | 0   | 0.4           | ns   |

| t                | HIGH-to-LOW                            | from (input) S1 or D1               | 0    | 1.3           | .3 0 | 1.3           | 0   | 0.8           | ne   |

| $t_{\rm PHL}$    | propagation delay                      | to (output) S2 or D2                | 0    | 1.5           |      |               |     |               | ns   |

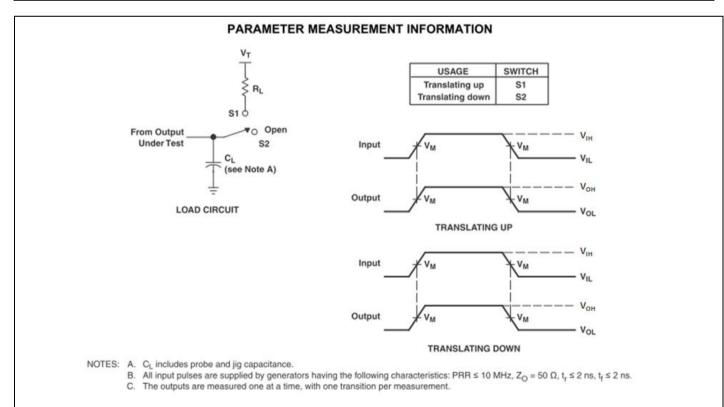

#### Figure 2. Load Circuit for Outputs

| A Product Line of<br>Diodes Incorporated | ()) PER |

|------------------------------------------|---------|

|------------------------------------------|---------|

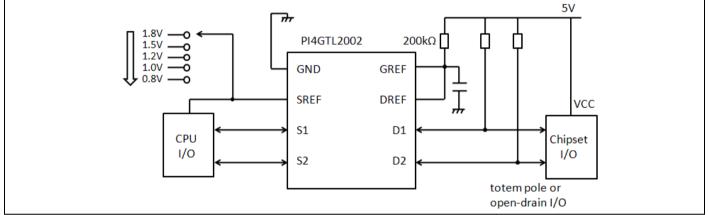

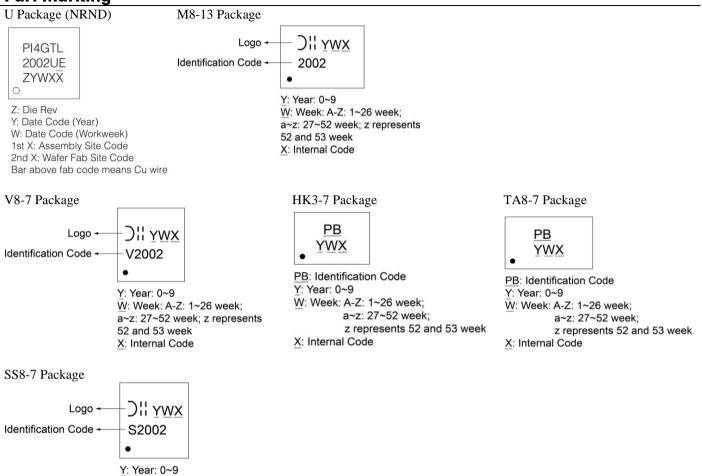

# **Application Information**

For the bidirectional clamping configuration, higher voltage to lower voltage or lower voltage to higher voltage, the GREF input must be connected to DREF and both pins pulled to HIGH side VCC through a pull-up resistor (typically 200k $\Omega$ ). A filter capacitor on DREF is recommended. The processor output can be totem pole or open-drain (pull-up resistors may be required) and the chip set output can be totem pole or open-drain (pull-up resistors are required to pull the Dn outputs to VCC). However, if either output is totem pole, data must be unidirectional or the outputs must be 3-stateable and the outputs must be controlled by some direction control mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open-drain, no direction control is needed. The opposite side of the reference transistor (SREF) is connected to the processor core power supply voltage. When DREF is connected through a 200k $\Omega$  resistor to a 3.3V to 5.5V VCC supply and SREF is set between 0.8V to (VCC - 1.5V), the output of each Sn has a maximum output voltage equal to SREF and the output of each Dn has a maximum output voltage equal to VCC.

Figure 3. Bidirectional Translation to Multiple Higher Voltage Levels Such as An I2c-Bus Application

For unidirectional clamping, higher voltage to lower voltage, the GREF input must be connected to DREF and both pins pulled to the higher side VCC through a pull-up resistor (typically  $200k\Omega$ ). A filter capacitor on DREF is recommended. Pull-up resistors are required if the chip set I/O are open-drain. The opposite side of the reference transistor (SREF) is connected to the processor core supply voltage. When DREF is connected through a  $200k\Omega$  resistor to a 3.3V to 5.5V VCC supply and SREF is set between 0.8V to (VCC-1.5V), the output of each Sn has a maximum output voltage equal to SREF.

Figure 4. Unidirectional Down Translation to Protect Low Voltage Processor Pins

For unidirectional up translation, lower voltage to higher voltage, the reference transistor is connected the same as for a down translation. A pull-up resistor is required on the higher voltage side (Dn or Sn) to get the full HIGH level, since the GTL-TVC device will only pass the reference source (SREF) voltage as a HIGH when doing an up translation. The driver on the lower voltage side only needs pull-up resistors if it is open-drain.

Figure 5. Unidirectional Down Translation to Protect Higher Voltage Processor Pins

# **Pull-up Resistors and Minimum Values**

Sizing the pull-up resistor on an open-drain bus is specific to the individual application and is dependent on the following driver characteristics:

- The driver sink current

- The V<sub>OL</sub> of driver

- The V<sub>OL</sub> of the PI4GTL2002

- The V<sub>IL</sub> of the driver

- Frequency of operation

The pull-up resistor value needs to limit the current through the pass transistor when it is in the ON state to about 15mA. This will guarantee a pass voltage of 260mV to 350mV.

If the current through the pass transistor is higher than 15mA, the pass voltage will also be higher in the ON state. To set the current through each pass transistor at 15mA, the pull-up resistor value is calculated as shown below:

Pull-up voltage (V) – 0.35V

Resistor Value =

0.015A

The following tables can be used to estimate the pull-up resistor value in different use cases so that the minimum resistance for the pull-up resistor can be found.

Tables in bellow contain suggested minimum values of pull-up resistors for the PI4GTL2002 with typical voltage translation levels and drive currents.

The calculated values assume that both drive currents are the same.

$V_{OL} = V_{IL} = 0.1*VCC$  and accounts for a 10 % VCC tolerance of the supplies, 1 % resistor values. It should be noted that the resistor chosen in the final application should be equal to or larger than the values shown in the table to ensure that the pass voltage is less than 10 % of the VCC voltage, and the external driver should be able to sink the total current from both pull-up resistors.

| ODEE C: 1. |                                                                                  |                                                                                            | <b>DREF Side</b>                                                                       |                                                                                        |                                                                  |

|------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------|

| SREF Side  | 1.5V                                                                             | 1.8V                                                                                       | 2.5V                                                                                   | 3.3V                                                                                   | 5.0V                                                             |

| 0.8V       | $\begin{aligned} R_{PU(S)} &= 825\Omega \\ R_{PU(D)} &= 825\Omega \end{aligned}$ | $\begin{split} R_{PU(S)} &= 936\Omega \\ R_{PU(D)} &= 936\Omega \end{split}$               | $R_{PU(S)} = none$ $R_{PU(D)} = 899\Omega$ Or both 1.20kΩ                              | $R_{PU(S)} = none$ $R_{PU(D)} = 1.20k\Omega$ Or both 1.49kΩ                            | $R_{PU(S)} = none$ $R_{PU(D)} = 1.83k\Omega$ Or both 2.12k\Omega |

| 1.0V       | $\begin{aligned} R_{PU(S)} &= 892\Omega \\ R_{PU(D)} &= 892\Omega \end{aligned}$ | $\begin{aligned} R_{PU(S)} &= 1k\Omega \\ R_{PU(D)} &= 1k\Omega \end{aligned}$             | $R_{PU(S)} = none$ $R_{PU(D)} = 892\Omega$ Or both 1.26kΩ                              | $R_{PU(S)} = none$ $R_{PU(D)} = 1.19k\Omega$ Or both 1.56kΩ                            | $R_{PU(S)} = none$ $R_{PU(D)} = 1.82k\Omega$ Or both 2.19k\Omega |

| 1.2V       |                                                                                  | $\begin{split} R_{\rm PU(S)} &= 1.07 k\Omega \\ R_{\rm PU(D)} &= 1.07 k\Omega \end{split}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 886\Omega$ Or both 1.33kΩ                              | $R_{PU(S)} = none$ $R_{PU(D)} = 1.18k\Omega$ Or both 1.63kΩ                            | $R_{PU(S)} = none$ $R_{PU(D)} = 1.81k\Omega$ Or both 2.26kΩ      |

| 1.5V       |                                                                                  |                                                                                            | $R_{PU(S)} = none$ $R_{PU(D)} = 875\Omega$ Or both 1.43kΩ                              | $R_{PU(S)} = none$ $R_{PU(D)} = 1.17k\Omega$ Or both 1.73kΩ                            | $R_{PU(S)} = none$ $R_{PU(D)} = 1.8k\Omega$ Or both 2.36k\Omega  |

| 1.8V       |                                                                                  |                                                                                            | $\begin{aligned} R_{PU(S)} &= 1.53 k\Omega \\ R_{PU(D)} &= 1.53 k\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 1.16k\Omega$ Or both 1.82kΩ                            | $R_{PU(S)} = none$ $R_{PU(D)} = 1.79 k\Omega$ Or both 2.46kΩ     |

| 2.5V       |                                                                                  |                                                                                            |                                                                                        | $\begin{aligned} R_{PU(S)} &= 2.06 k\Omega \\ R_{PU(D)} &= 2.06 k\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 1.77 k\Omega$ Or both 2.69kΩ     |

| 3.3V       |                                                                                  |                                                                                            |                                                                                        |                                                                                        | $R_{PU(S)} = none$ $R_{PU(D)} = 1.74k\Omega$ Or both 2.96kΩ      |

Pull-up Resistor Minimum Values, 3 mA Driver /Sink Current for PI4GTL2002

### Pull-up Resistor Minimum Values, 10 mA Driver/ Sink Current for PI4GTL2002

| SREF Side |                                                                                  |                                                                                  | <b>DREF Side</b>                                                                 |                                                                                  |                                                                                                  |

|-----------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| SKEF SIde | 1.5V                                                                             | 1.8V                                                                             | 2.5V                                                                             | 3.3V                                                                             | 5.0V                                                                                             |

| 0.8V      | $\begin{aligned} R_{PU(S)} &= 247\Omega \\ R_{PU(D)} &= 247\Omega \end{aligned}$ | $\begin{split} R_{PU(S)} &= 281\Omega \\ R_{PU(D)} &= 281\Omega \end{split}$     | $R_{PU(S)} = none$ $R_{PU(D)} = 270\Omega$ Or both 359Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 359\Omega$ Or both 447 $\Omega$                  | $\begin{aligned} R_{PU(S)} &= none \\ R_{PU(D)} &= 547\Omega \\ Or both 636\Omega \end{aligned}$ |

| 1.0V      | $\begin{aligned} R_{PU(S)} &= 268\Omega \\ R_{PU(D)} &= 268\Omega \end{aligned}$ | $\begin{array}{l} R_{PU(S)}{=}300\Omega \\ R_{PU(D)}{=}300\Omega \end{array}$    | $R_{PU(S)} = none$ $R_{PU(D)} = 268\Omega$ Or both 379Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 357\Omega$ Or both 468 $\Omega$                  | $\begin{aligned} R_{PU(S)} &= none \\ R_{PU(D)} &= 545\Omega \\ Or both 657\Omega \end{aligned}$ |

| 1.2V      |                                                                                  | $\begin{aligned} R_{PU(S)} &= 321\Omega \\ R_{PU(D)} &= 321\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 266\Omega$ Or both 399Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 355\Omega$ Or both 488Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 543\Omega$ Or both 677 $\Omega$                                  |

| 1.5V      |                                                                                  |                                                                                  | $R_{PU(S)} = none$ $R_{PU(D)} = 263\Omega$ Or both 429 $\Omega$                  | $R_{PU(S)} = none$ $R_{PU(D)} = 352\Omega$ Or both 518Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 540\Omega$ Or both 707 $\Omega$                                  |

| 1.8V      |                                                                                  |                                                                                  | $\begin{aligned} R_{PU(S)} &= 460\Omega \\ R_{PU(D)} &= 460\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 348\Omega$ Or both 548Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 537\Omega$ Or both 737Ω                                          |

| 2.5V      |                                                                                  |                                                                                  |                                                                                  | $\begin{aligned} R_{PU(S)} &= 619\Omega \\ R_{PU(D)} &= 619\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 521\Omega$ Or both 808Ω                                          |

| 3.3V      |                                                                                  |                                                                                  |                                                                                  |                                                                                  | $R_{PU(S)} = none$ $R_{PU(D)} = 522\Omega$ Or both 889Ω                                          |

| ODEE C: 1 |                                                                                  |                                                                                  | <b>DREF Side</b>                                                                 |                                                                              |                                                                 |

|-----------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------|

| SREF Side | 1.5V                                                                             | 1.8V                                                                             | 2.5V                                                                             | 3.3V                                                                         | 5.0V                                                            |

| 0.8V      | $\begin{aligned} R_{PU(S)} &= 165\Omega \\ R_{PU(D)} &= 165\Omega \end{aligned}$ | $\begin{split} R_{PU(S)} &= 187\Omega \\ R_{PU(D)} &= 187\Omega \end{split}$     | $R_{PU(S)} = none$ $R_{PU(D)} = 180\Omega$ Or both 239 $\Omega$                  | $R_{PU(S)} = none$ $R_{PU(D)} = 239\Omega$ Or both 298Ω                      | $R_{PU(S)} = none$ $R_{PU(D)} = 365\Omega$ Or both 424 $\Omega$ |

| 1.0V      | $\begin{aligned} R_{PU(S)} &= 178\Omega \\ R_{PU(D)} &= 178\Omega \end{aligned}$ | $\begin{split} R_{PU(S)} &= 200\Omega \\ R_{PU(D)} &= 200\Omega \end{split}$     | $R_{PU(S)} = none$ $R_{PU(D)} = 178\Omega$ Or both 253Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 237\Omega$ Or both 312Ω                      | $R_{PU(S)} = none$ $R_{PU(D)} = 364\Omega$ Or both 438\Omega    |

| 1.2V      |                                                                                  | $\begin{aligned} R_{PU(S)} &= 214\Omega \\ R_{PU(D)} &= 214\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 177\Omega$ Or both 266Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 236\Omega$ Or both 325Ω                      | $R_{PU(S)} = none$ $R_{PU(D)} = 362\Omega$ Or both 451\Omega    |

| 1.5V      |                                                                                  |                                                                                  | $R_{PU(S)} = none$ $R_{PU(D)} = 175\Omega$ Or both 286Ω                          | $R_{PU(S)} = none$ $R_{PU(D)} = 234\Omega$ Or both 345Ω                      | $R_{PU(S)} = none$ $R_{PU(D)} = 360\Omega$ Or both 471\Omega    |

| 1.8V      |                                                                                  |                                                                                  | $\begin{aligned} R_{PU(S)} &= 306\Omega \\ R_{PU(D)} &= 306\Omega \end{aligned}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 232\Omega$ Or both 366 $\Omega$              | $R_{PU(S)} = none$ $R_{PU(D)} = 358\Omega$ Or both 492\Omega    |

| 2.5V      |                                                                                  |                                                                                  |                                                                                  | $\begin{split} R_{PU(S)} &= 413\Omega \\ R_{PU(D)} &= 413\Omega \end{split}$ | $R_{PU(S)} = none$ $R_{PU(D)} = 354\Omega$ Or both 539\Omega    |

| 3.3V      |                                                                                  |                                                                                  |                                                                                  |                                                                              | $R_{PU(S)} = none$ $R_{PU(D)} = 348\Omega$ Or both 593\Omega    |

Pull-up Resistor Minimum Values, 15 mA Driver/ Sink Current for PI4GTL2002

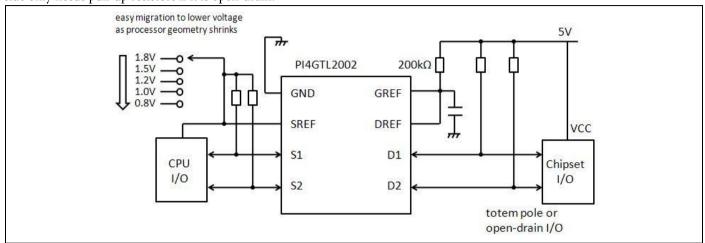

### **Part Marking**

<u>Y</u>: Year: 0~9 <u>W</u>: Week: A-Z: 1~26 week; a~z: 27~52 week; z represents 52 and 53 week <u>X</u>: Internal Code

Тур

0.10

0.86

0.39

0.30

0.15

3.00

4.90

3.00

2.95

0.65

0.60

4°

0.750

0.750

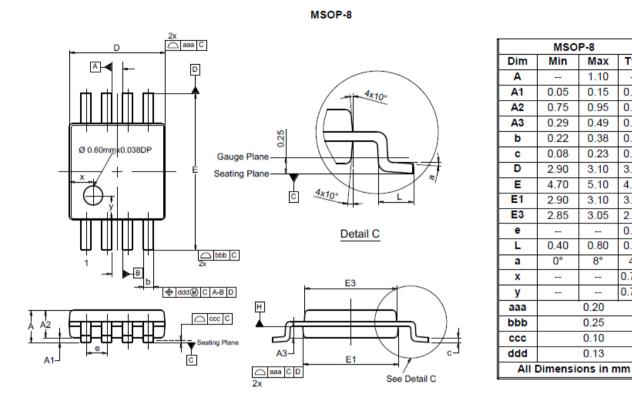

# **Packaging Mechanical**

8-MSOP (M)

# **Package Outline Dimensions**

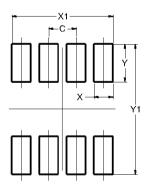

| Suggested Pad Layou | t |

|---------------------|---|

|---------------------|---|

MSOP-8

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.650            |

| X          | 0.450            |

| Y          | 1.350            |

| Y1         | 5.300            |

A Product Line of Diodes Incorporated

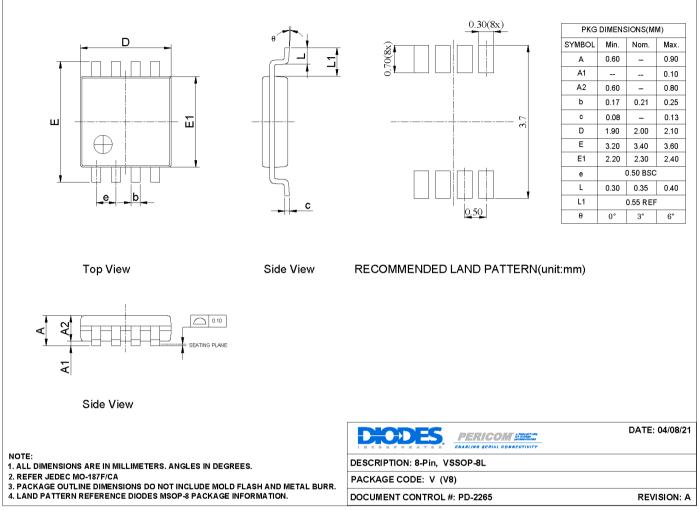

#### 8-VSSOP (V)

21-1396

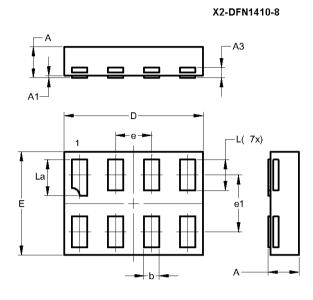

### 8-X2-DFN (HK)

# Package Outline Dimensions

| X2-DFN1410-8         |      |      |      |

|----------------------|------|------|------|

| Dim                  | Min  | Max  | Тур  |

| Α                    | 0.30 | 0.35 | 0.33 |

| A1                   | 0.00 | 0.03 | 0.02 |

| A3                   |      |      | 0.10 |

| b                    | 0.12 | 0.20 | 0.15 |

| D                    | 1.30 | 1.40 | 1.35 |

| Е                    | 0.95 | 1.05 | 1.00 |

| е                    |      |      | 0.35 |

| e1                   |      |      | 0.55 |

| L                    | 0.27 | 0.35 | 0.30 |

| L1                   | 0.32 | 0.40 | 0.35 |

| All Dimensions in mm |      |      |      |

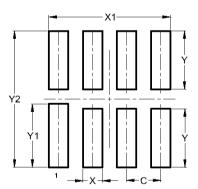

# Suggested Pad Layout

X2-DFN1410-8

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.350            |

| X          | 0.200            |

| X1         | 1.250            |

| Y          | 0.600            |

| Y1         | 0.650            |

| Y2         | 1.400            |

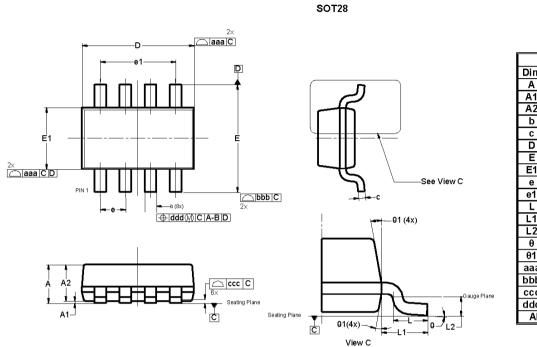

### 8-SOT28 (TA)

# Package Outline Dimensions

|                      | SOT28     |      |      |  |

|----------------------|-----------|------|------|--|

| Dim                  | Min       | Max  | Тур  |  |

| Α                    | 0.90      | 1.10 | 1.00 |  |

| A1                   | 0.00      | 0.10 |      |  |

| A2                   |           |      | 0.95 |  |

| b                    | 0.20      | 0.40 | 0.30 |  |

| С                    | 0.08 0.20 |      |      |  |

| D                    | 2.85      | 2.95 | 2.90 |  |

| Е                    | 2.65      | 2.95 | 2.80 |  |

| E1                   | 1.55      | 1.65 | 1.60 |  |

| е                    | 0.65 BSC  |      |      |  |

| e1                   | 1.95 BSC  |      |      |  |

| L                    | 0.30      | 0.60 | 0.45 |  |

| L1                   | 0.60 REF  |      |      |  |

| L2                   | 0.25 BSC  |      |      |  |

| θ                    | 0°        | 8°   |      |  |

| θ1                   | 9°        | 11°  | 10°  |  |

| aaa                  | 0.15      |      |      |  |

| bbb                  | 0.25      |      |      |  |

| CCC                  | 0.10      |      |      |  |

| ddd                  | 0.20      |      |      |  |

| All Dimensions in mm |           |      |      |  |

# **Suggested Pad Layout**

SOT28

| Dimensions | Value   |

|------------|---------|

|            | (in mm) |

| С          | 0.950   |

| G          | 1.600   |

| Х          | 0.700   |

| Y          | 0.900   |

| Y1         | 3.400   |

A Product Line of Diodes Incorporated

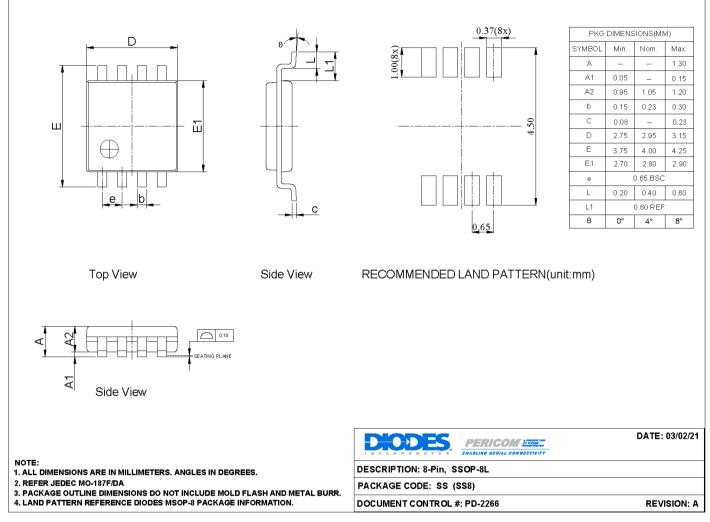

#### 8-SSOP (SS)

21-1374

For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Part Numbers    | Package Code | Package Description                                                       |

|-----------------|--------------|---------------------------------------------------------------------------|

| PI4GTL2002UEX   | U            | 8-Pin, Mini Small Outline Package (MSOP) (Not Recommended for New Design) |

| PI4GTL2002M8-13 | М            | 8-Pin, Mini Small Outline Package (MSOP)                                  |

| PI4GTL2002V8-7  | V            | 8-Pin (VSSOP)                                                             |

| PI4GTL2002HK3-7 | HK           | 8-Pin (X2-DFN1410)                                                        |

| PI4GTL2002TA8-7 | TA           | 8-Pin (SOT28)                                                             |

| PI4GTL2002SS8-7 | SS           | 8-Pin (SSOP)                                                              |

#### Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. 7 = Tape/Reel size (7"), X suffix = Tape/Reel

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-and-conditions/terms-a

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/importantnotice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

www.diodes.com