## **PI4IOE5V9520**

# Remote 2-bit I<sup>2</sup>C-bus low power I/O port with interrupt and reset

#### **Features**

- → Operation power supply voltage from 2.3V to 5.5V

- → 2-bit I<sup>2</sup>C-bus GPIO with interrupt and reset

- → 5V tolerant I/Os

- → Active Low interrupt output

- → Active Low reset input

- → Low current consumption

- → 0Hz to 1MHz clock frequency

- → Noise filter on SCL/SDA inputs

- → Power-on reset, software reset

- → ESD protection (4KV HBM and 1KV CDM)

- → Package offered: UQFN 1.6x1.6-8

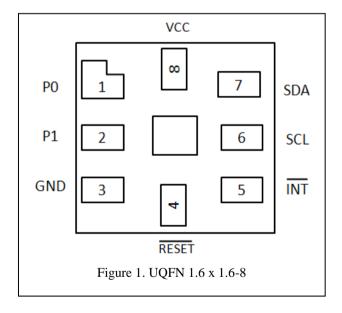

## **Pin Configuration**

# **Description**

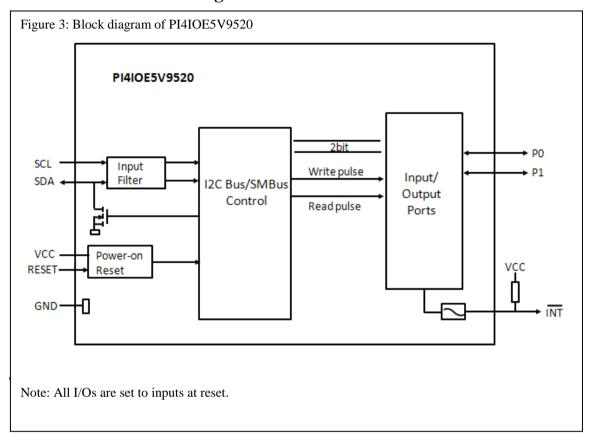

The PI4IOE5V9520 provides 2 bits of General Purpose parallel Input/Output (GPIO) expansion for I<sup>2</sup>C-bus applications. It includes the features such as higher driving capability, 5V tolerance, lower power supply, individual I/O configuration, and smaller packaging. It provides a simple solution when additional I/O is needed for ACPI power switches, sensors, push buttons, LEDs, fans, etc.

The PI4IOE5V9520 consists of a 2-bit quasi-bidirectional port and an I<sup>2</sup>C-bus interface.

The PI4IOE5V9520 open-drain interrupt output (INT) is activated by any updated of the port inputs and is used to indicate the system master that the port inputs has changed.

The power-on reset sets the registers to their default values and initializes the device state machine. The Reset pin (Reset) causes the same reset/initialization to occur without de-powering the device.

# **Pin Description**

Table 1. Pin description

| Pin | Name  | Туре | Description                   |

|-----|-------|------|-------------------------------|

| 1   | Р0    | I/O  | Input/Output 0                |

| 2   | P1    | I/O  | Input/Output1                 |

| 3   | GND   | G    | Supply ground                 |

| 4   | RESET | I    | Reset pin                     |

| 5   | INT   | О    | Interrupt output (open-drain) |

| 6   | SCL   | I    | Serial clock line             |

| 7   | SDA   | I/O  | Serial data line              |

| 8   | VCC   | P    | Power supply                  |

<sup>\*</sup> I = Input; O = Output; P = Power; G = Ground

# **Maximum Ratings**

| Power supply                           | 0.5V to +6.0V     |

|----------------------------------------|-------------------|

| Voltage on an I/O pin                  | GND-0.5V to +6.0V |

| Input current                          | ±20mA             |

| Output current on an I/O pin           | ±50mA             |

| Supply current                         | 40mA              |

| Ground supply current                  | 50mA              |

| Total power dissipation                | 200mW             |

| Operation temperature                  | 40~85°C           |

| Storage temperature                    | 65~150°C          |

| Maximum Junction temperature ,T j(max) | 125°C             |

|                                        |                   |

#### Note

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Static characteristics**

VCC = 2.3 V to 5.5 V; GND = 0 V;  $Tamb = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ ; unless otherwise specified.

Table 2: Static characteristics

| Symbol           | Parameter                             | Conditions                                                                 | Min.   | Тур. | Max.    | Unit |

|------------------|---------------------------------------|----------------------------------------------------------------------------|--------|------|---------|------|

| Power suj        | pply                                  |                                                                            | •      |      |         |      |

| VCC              | Supply voltage                        |                                                                            | 2.3    | -    | 5.5     | V    |

| $I_{CC}$         | Supply current                        | Operating mode; VCC = 5.5 V; no load; fSCL= 100 kHz                        | -      | 104  | 175     | μΑ   |

| $I_{stb}$        | Standby current                       | Standby mode; VCC = 5.5 V; no load;<br>VI = VCC; fSCL= 0 kHz; I/O = inputs |        | 0.25 | 1       | μΑ   |

| V <sub>POR</sub> | Power-on reset voltage <sup>[1]</sup> |                                                                            | -      | 1.16 | 1.41    | V    |

| Input SC         | L, input/output SDA                   |                                                                            |        |      |         |      |

| $V_{I\!L}$       | Low level input voltage               |                                                                            | -0.5   | -    | +0.3VCC | V    |

| V <sub>IH</sub>  | High level input voltage              |                                                                            | 0.7VCC | -    | 5.5     | V    |

| $I_{OL}$         | Low level output current              | $V_{OL}=0.4V$                                                              | 20     | -    | -       | mA   |

| $I_L$            | Leakage current                       | $V_I = VCC = GND$                                                          | -1     | -    | 1       | μΑ   |

| $C_{i}$          | Input capacitance                     | $V_I = GND$                                                                | -      | 5    | 10      | pF   |

# $\label{eq:Remote 2-bit I^2C-bus} Remote \ 2\text{-bit I}^2C\text{-bus} \\ low \ power \ I/O \ port \ with \ interrupt \ and \ reset \\$

| Symbol                | Parameter                         | Conditions                                          | Min. | Тур. | Max.  | Unit |  |  |

|-----------------------|-----------------------------------|-----------------------------------------------------|------|------|-------|------|--|--|

| I/Os                  |                                   |                                                     |      |      |       |      |  |  |

| VIL                   | Low level input voltage           |                                                     | -0.5 | -    | +0.81 | V    |  |  |

| VIH                   | High level input voltage          |                                                     | +1.8 | -    | 5.5   | V    |  |  |

|                       |                                   | $VCC = 2.3 \text{ V}; V_{OL} = 0.5 \text{ V}^{[2]}$ | 12   | 28   | -     | mA   |  |  |

| $I_{OL}$              | Low level output voltage current  | $VCC = 3.0V; V_{OL} = 0.5 V^{[2]}$                  | 17   | 35   | -     | mA   |  |  |

|                       |                                   | $VCC = 4.5 \text{ V}; V_{OL} = 0.5 \text{ V}^{[2]}$ | 25   | 42   | =     | mA   |  |  |

| I <sub>OL</sub> (tot) | Total LOW-level output current    | $V_{OL} = 0.5V; VCC = 4.5V$                         |      |      | 50    | mA   |  |  |

| $I_{OH}$              | HIGH-level output current         | $V_{OH} = GND$                                      | -30  | -359 | -480  | uA   |  |  |

| Itrt(pu)              | Transient boosted pull-up current | $V_{OH} = GND$                                      | -0.5 | -1.0 |       | mA   |  |  |

| $C_{i}$               | Off-state Input capacitance       |                                                     | -    | 9    | 10    | pF   |  |  |

| Co                    | Off-state Output capacitance      |                                                     | -    | 9    | 10    | pF   |  |  |

| Interrupt             | INT                               |                                                     |      |      |       |      |  |  |

| $I_{OL}$              | Low level input voltage           | $V_{OL} = 0.4V$                                     | 3    | 13   | -     | mA   |  |  |

| $I_{OH}$              | High level input voltage          | $V_{OL} = 0.4V$                                     | -1   |      | +1    | uA   |  |  |

| Reset RE              | Reset RESET                       |                                                     |      |      |       |      |  |  |

| V <sub>IL</sub>       | Low level input voltage           |                                                     | -0.5 | -    | +0.81 | V    |  |  |

| $V_{\mathrm{IH}}$     | High level input voltage          |                                                     | +1.8 | -    | 5.5   | V    |  |  |

| $I_L$                 | Input leakage current             | $V_I = VCC = GND$                                   | -1   |      | 1     | μΑ   |  |  |

#### Note:

[1]: VCC must be lowered to 0.2 V for at least 5 us in order to reset part.

<sup>[2]:</sup> Each I/O must be externally limited to a maximum of 25 mA and the total package must be limited to a maximum current of 50 mA.

# **Dynamic characteristics**

Table 3: Dynamic characteristics

| Symbol                             | Parameter                                                         | Conditions | Standard mode<br>I <sup>2</sup> C |      | Fast mode<br>I <sup>2</sup> C |     | Fast mode Plus<br>I <sup>2</sup> C |      | Unit |

|------------------------------------|-------------------------------------------------------------------|------------|-----------------------------------|------|-------------------------------|-----|------------------------------------|------|------|

| Symbol                             | Turumeer                                                          | Conditions | Min                               | Max  | Min                           | Max | Min                                | Max  |      |

| $f_{SCL}$                          | SCL clock frequency                                               |            | 0                                 | 100  | 0                             | 400 | 0                                  | 1000 | kHz  |

| $t_{ m BUF}$                       | Bus free time between a STOP and START condition                  |            | 4.7                               | -    | 1.3                           | -   | 0.5                                | -    | μs   |

| t <sub>HD;STA</sub>                | Hold time (repeated) START condition                              |            | 4.0                               | -    | 0.6                           | -   | 0.26                               | -    | μs   |

| t <sub>SU;STA</sub>                | Set-up time for a repeated START condition                        |            | 4.7                               | -    | 0.6                           | -   | 0.26                               | -    | μs   |

| $t_{\mathrm{SU;STO}}$              | Set-up time for STOP condition                                    |            | 4.0                               | -    | 0.6                           | -   | 0.26                               | -    | μs   |

| t <sub>VD;ACK</sub> <sup>[1]</sup> | Data valid acknowledge time                                       |            | -                                 | 3.45 | -                             | 0.9 | -                                  | 0.45 | μs   |

| t <sub>HD;DAT</sub> <sup>[2]</sup> | Data hold time                                                    |            | 0                                 | -    | 0                             | -   | 0                                  | -    | ns   |

| t <sub>VD;DAT</sub>                | Data valid time                                                   |            | -                                 | 3.45 | -                             | 0.9 | -                                  | 0.45 | us   |

| $t_{SU;DAT}$                       | Data set-up time                                                  |            | 250                               | -    | 100                           | -   | 50                                 | -    | ns   |

| $t_{LOW}$                          | LOW period of the SCL clock                                       |            | 4.7                               | -    | 1.3                           | -   | 0.5                                | -    | μs   |

| t <sub>HIGH</sub>                  | HIGH period of the SCL clock                                      |            | 4.0                               | -    | 0.6                           | -   | 0.26                               | -    | μs   |

| $t_{ m f}$                         | Fall time of both SDA and SCL signals                             |            | -                                 | 300  | -                             | 300 | -                                  | 120  | ns   |

| $t_{\rm r}$                        | Rise time of both SDA and SCL signals                             |            | -                                 | 1000 | -                             | 300 | -                                  | 120  | ns   |

| $t_{SP}$                           | Pulse width of spikes that must be suppressed by the input filter |            | -                                 | 50   | -                             | 50  |                                    | 50   | ns   |

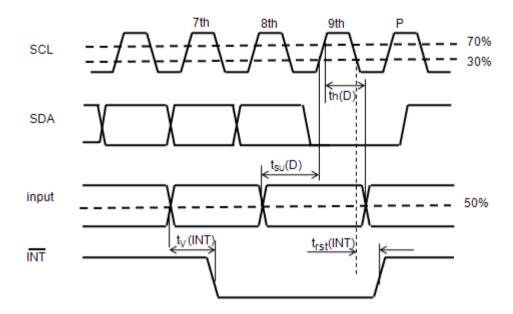

| Port timin                         | g                                                                 |            |                                   |      |                               |     |                                    |      |      |

| $t_{v(Q)}$                         | Data output valid time <sup>[3]</sup>                             |            | -                                 | 200  | -                             | 200 | -                                  | 200  | ns   |

| t <sub>su(D)</sub>                 | Data input set-up time                                            |            | 100                               | -    | 100                           | -   | 100                                | -    | ns   |

| t <sub>h(D)</sub>                  | Data input hold time                                              |            | 1                                 | -    | 1                             | -   | 1                                  | -    | μs   |

| Interrupt                          | timing                                                            |            |                                   |      |                               |     |                                    |      |      |

| t <sub>v(INT)</sub>                | Valid time on pin INT                                             |            | -                                 | 4    | -                             | 4   | -                                  | 4    | μs   |

| t <sub>rst(INT)</sub>              | Reset time on pin INT                                             |            | -                                 | 4    | -                             | 4   | -                                  | 4    | μs   |

# Remote 2-bit I<sup>2</sup>C-bus low power I/O port with interrupt and reset

| Symbol           | mbol Parameter                     |            | Standard mode<br>I <sup>2</sup> C |     | Fast mode<br>I <sup>2</sup> C |     | Fast mode Plus<br>I <sup>2</sup> C |     | Unit |

|------------------|------------------------------------|------------|-----------------------------------|-----|-------------------------------|-----|------------------------------------|-----|------|

| Symbol           | i arametei                         | Conditions | Min                               | Max | Min                           | Max | Min                                | Max |      |

| Reset timi       | Reset timing                       |            |                                   |     |                               |     |                                    |     |      |

| $t_{w(rst)}$     | Reset pulse width                  |            | 25                                | -   | 25                            | -   | 25                                 | -   | ns   |

| $t_{rec(rst)}$   | Reset recovery time <sup>[4]</sup> |            | 0                                 | -   | 0                             | -   | 0                                  | -   | ns   |

| t <sub>rst</sub> | Reset time                         |            | 1                                 | -   | 1                             | 1   | 1                                  | 1   | us   |

#### Note:

- [1]:  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW.

- [2]:  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW.

- [3]:  $t_{v(O)}$  measured from 0.7VCC on SCL to 50% I/O output.

PERICOM®

[4]: To reset the device while actively communicating on the bus may cause glitches or errant STOP conditions. Upon reset, the full delay will be the sum of  $t_{rst}$  and RC time constant of SDA bus.

Figure 2: Timing diagram for INT timing and Port timing

# PI4IOE5V9520 Block Diagram

# **Details Description**

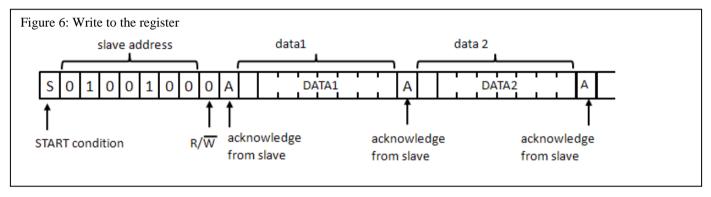

### a. Device address

Table 4: Device address

|              | b7(MSB) | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

|--------------|---------|----|----|----|----|----|----|-----|

| Address Byte | 0       | 1  | 0  | 0  | 1  | 0  | 0  | R/W |

Note: Read "1", Write "0"

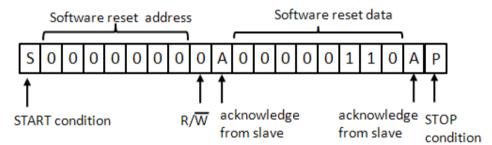

## **b. Software Reset Call**

General Call address: allows resetting the device through the I<sup>2</sup>C-bus upon reception of the right I<sup>2</sup>C-bus sequence.

|                         | b7(MSB) | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-------------------------|---------|----|----|----|----|----|----|----|

| General Call<br>Address | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

### c. Software Reset

The Software Reset Call allows all the devices in the  $I^2C$ -bus to be reset to the power-up state value through a specific formatted  $I^2C$ -bus command. To be performed correctly, it implies that the  $I^2C$ -bus is functional and that there is no device hanging the bus.

The Software Reset sequence is defined as following:

- 1. A START command is sent by the I<sup>2</sup>C-bus master.

- 2. The reserved General Call I<sup>2</sup>C-bus address '0000 000' with the R/W bit set to 0 (write) is sent by the I<sup>2</sup>C-bus master.

- 3. The device acknowledges after seeing the General Call address '0000 0000' (00h) only. If the R/W bit is set to 1 (read), no acknowledge is returned to the  $I^2C$ -bus master.

- 4. Once the General Call address has been sent and acknowledged, the master sends 1 byte. The value of the byte must be equal to 06h.

- a. The device acknowledges this value only. If the byte is not equal to 06h, the device does not acknowledge it.

- b. If more than 1 byte of data is sent, the device does not acknowledge any more.

- 5. Once the right byte has been sent and correctly acknowledged, the master sends a STOP command to end the Software Reset sequence: the device then resets to the default value (power-up value) and is ready to be addressed again within the specified bus free time. If the master sends a Repeated START instead, no reset is performed.

The I<sup>2</sup>C-bus master must interpret a non-acknowledge from the device (at any time) as a 'Software Reset Abort'. The device does not initiate a reset of its registers.

The unique sequence that initiates a Software Reset is described in Figure 4.

Figure 4: Software reset

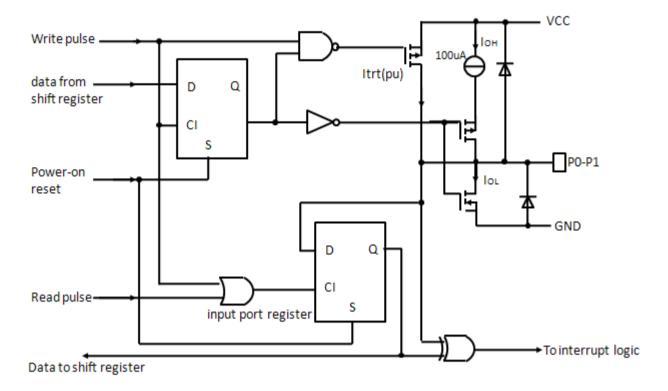

#### d. Quasi-bidirectional I/O architecture

The device ports are entirely independent and are output ports. The state of the ports at the pin is transferred from the ports to the microcontroller in the Read mode (see Figure 7). Output data is transmitted to the ports in the Write mode (see Figure 6). At power-on all ports are HIGH. A bit set to 1 in the data byte drives the line HIGH at the corresponding port. A bit set to 0 in the data byte drives the line LOW at the corresponding port.

If an external voltage is applied to an output, care should be exercised because of the low-impedance path that exists between the pin and either VCC or GND.

Figure 5:I/O architecture

#### e. Bus Transaction

#### Writing to the port (output mode)

To write, the master (microcontroller) first addresses the slave device. By setting the last bit of the byte containing the slave address to logic 0, the Write mode is entered. The device acknowledges and the master sends the data byte for P7 to P0 and is acknowledged by the device. Writes to P7 to P2 are ignored in the PI4IOE5V9520 as only P1 through P0 are available. The 2-bit data is presented on the port lines after it has been acknowledged by the device. The number of data bytes that can be sent successively is not limited. The previous data is overwritten every time a data byte has been sent.

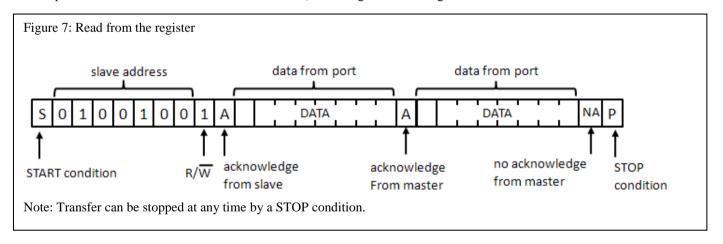

#### **Reading from a port (input mode)**

All ports are outputs and cannot be used as inputs. When reading the device, the data returned is the port state at the pin. To read, the master (microcontroller) first addresses the slave device by setting the last bit of the byte containing the slave address to logic 1. The data byte that follows on the SDA is the value of the ports pins. There is no limit to the number of bytes read, and the state of the output port pins is updated at each acknowledge cycle. Logic 1 means that the port is HIGH. Logic 0 means that the port is LOW. When the PI4IOE5V9520 is read, P7 through P2 return logic '1'.

#### f. Power-on reset

When power is applied to VCC, an internal Power-On Reset (POR) holds the device in a reset condition until VCC has reached VPOR. At that point, the reset condition is released and the device registers and I<sup>2</sup>C-bus state machine initialize to their default states.

# g. Interrupt output $(\overline{INT})$

The open-drain interrupt output  $(\overline{INT})$  is activated when one of the port pins changes state and the pin is configured as an input. The interrupt is de-activated when the input returns to its previous state or data is read from the device.

2016-02-0001 PT0563-1 3/29/16

# h. RESET input

A reset can be accomplished by holding the  $\overline{RESET}$  pin LOW for a minimum of  $t_{w(rst)}$ . The PI4IOE5V9520 registers and  $I^2C$ -bus state machine will be held in their default state until the  $\overline{RESET}$  input is once again HIGH.

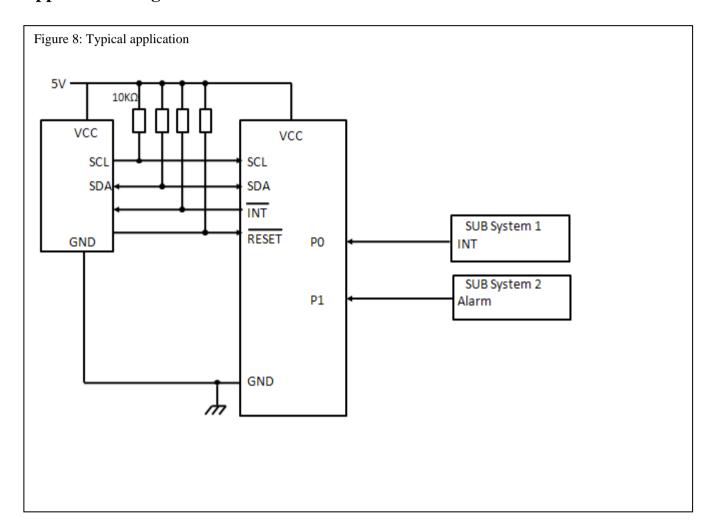

## **Application design-in information**

2016-02-0001 PT0563-1 3/29/16

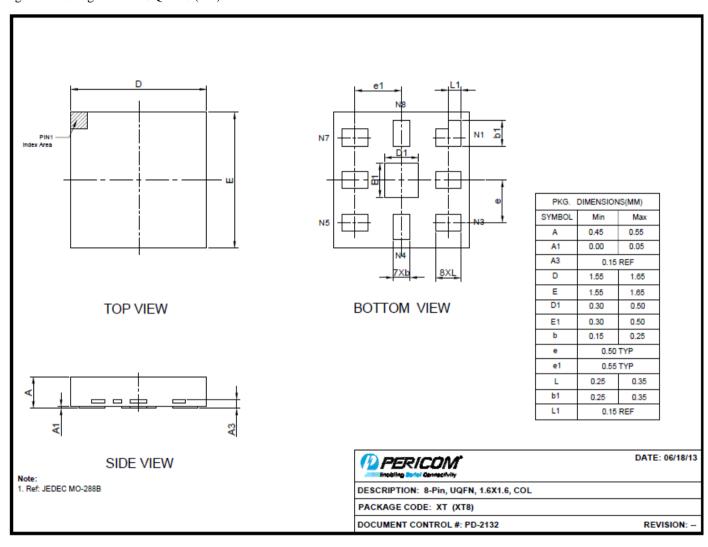

## **Mechanical Information**

UQFN-8 (XT)

Figure 9. Package outline UQFN-8 (XT)

# **Ordering Information**

| Part No.         | Package Code | Package                         |

|------------------|--------------|---------------------------------|

| PI4IOE5V9520XTEX | XT           | 8-pin UQFN 1.6x1.6, Tape & Reel |

#### Note:

- E = Pb-free and Green

- Adding X Suffix= Tape/Reel

#### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

Pericom reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom does not assume any responsibility for use of any circuitry described other than the circuitry embodied in Pericom product. The company makes no representations that circuitry described herein is free from patent infringement or other rights, of Pericom.

2016-02-0001 PT0563-1 3/29/16