BoM and PCB Space Savings Achieved with Control Channel Aggregation for Optical Interfaces

By Eric Lan, Assistant Product Marketing Manager of Connect ASIC Product Line

Introduction

Fibre optic networks bring the promise of fast broadband to new customers all around the world. It increasingly reaches new limits, but to provide a guaranteed level of service, that bandwidth must be managed effectively. A significant factor to that effectiveness is how it interfaces with other network equipment running over copper cable.

The preference for fibre is not just about speed. Fibre is much lighter and smaller than copper so operators can support more connections. It is effectively immune from electromagnetic interference (EMI) and is more secure than cable. Fibre also experiences much less attenuation than copper across a wide frequency band.

However, one disadvantage of fibre is space. Because the source electrical signal must convert to light, and back again, this requires a transceiver module near the edge of the PCB to terminate each end of the fibre for each channel. Each transceiver typically needs to be controlled via a serial interface, such as I2C. With all of these components, the multiple control channels required can be a struggle to fit within the available PCB space.

In this article, we’ll look at how design engineers can reduce the number of discrete components and board space. By using a multi-port expander that links to several transceivers, we can aggregate the serial control channels and help make layout easier, while also reducing the Bill of Materials (BoM) cost.

Controlling multiple optical transceivers

Transceivers are the interface between high-speed optical communications and the electrical parts in the network, including optical subassemblies for transmission and reception. By using a photoemitter or photoreceiver along with an arrangement of lenses, transceivers convert digital data to and from a light wave in the form of a pulsed laser.

Channels may aggregate together to achieve higher bandwidth, which means multiple transceivers are needed in the network, and possibly within a switch or router. As networks become more complex, the number of channels (and hence transceivers) grows to potentially unmanageable proportions.

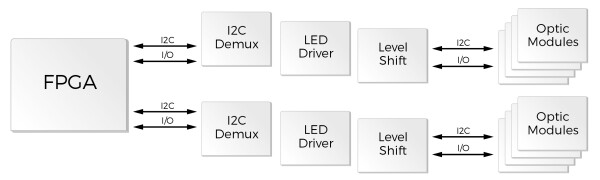

With a dedicated control path typically used for each channel, the space and power consumption required on the PCB can become unrealistically large. To limit this, the FPGA or ASIC being used to manage the transceivers will simply run out of suitable pins, as shown in figure 1 below.

Multi-port expanders to the rescue

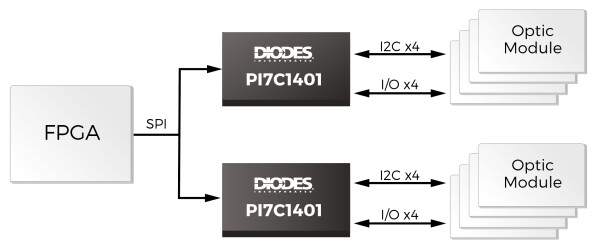

To overcome these issues, we can replace the multiple intermediary devices (I2C demultiplexer, LED driver and level shifter) with a single part that can control multiple modules, such as Diodes Incorporated’s PI7C1401 quad port expander (Figure 2).

Each quad-port expander provides aggregation of up to four I2C or SPI interfaces. So instead of dedicating a port to each interface, a single FPGA or ASIC can address and control a minimum of four optical modules with a single I2C/SPI interface (Figure 3).

Up to 14 PI7C1401 devices can be combined in a chain with their input wire-or’d together. This enables a host processor to control up to 56 transceivers through one I2C/SPI interface, thus significantly reducing pin-count minimums, PCB space requirements, and BoM cost.

As the host processor will usually operate at a high processing frequency, it easily handles multiple low-speed ports from a single interface. Because the capacity limit is usually based on pin count rather than processing performance, multiplexing several control ports through a single interface overcomes this restriction.

The devices automatically configure their addresses, so there is no need for each part to have a unique address. This gives an immediate increase in capacity and, where board space permits, enables extra optical modules to be fitted and controlled in an existing design.

Extended features

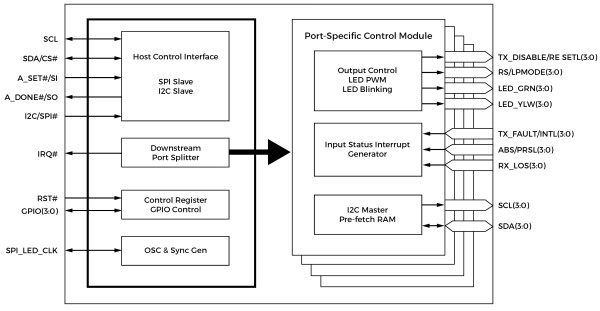

The PI7C1401 offers extended module management features, which can improve a system’s overall performance. Many of the control functions can also be offloaded onto the port expander, freeing up the host device to focus on other activities. This means a lower-price host processor can be selected, reducing both cost and the host’s routing layer congestion.

The speed of the host interface is selectable and dependent on the protocol being used. An I2C interface operates up to 1MHz, but when configured as an SPI interface, it runs up to 33MHz. The PI7C1401 also features GPIO pins that can be controlled by registers for management functions.

Some low-speed interface specifications, such as SFF-8472 and SFF-8431, define logical device addresses. For direct accesses, the PI7C1401 can use the address mapping scheme to enable the upstream host to issue downstream read-or-write operations. The port expander can also perform pre-fetch read operations from downstream modules.

This data is stored in the PI7C1401’s on-chip 32byte FIFO. The size and address of the data is configurable, and the pre-fetch operation can be scheduled or triggered by an interrupt. Direct accesses have a higher priority than a pre-fetch operation.

Conclusion

As fibre replaces copper throughout networks, optical interfaces are being used in increasing numbers. Managing this expansion requires dedicated control channels, which can rapidly consume PCB space.

Instead of using up resources by adding more control channels, designers can offload many port management tasks by using a port expander to handle these multiple channels. The host device better manages the routing layer tasks by raising the level of abstraction, and overall system efficiency increases while channel aggregation reduces board space requirements and overall system costs.